# Universidad Complutense de Madrid Departamento de Informática y Automática

# Técnicas de Estimación de Características Físicas en Síntesis de Alto Nivel Hortensia Mecha López

# **TESIS DOCTORAL**

Director: Dra. Milagros Fernández Centeno

Madrid, 1996

Memoria presentada por Hortensia Mecha López para optar al título de Doctor en Ciencias Físicas por la Universidad Complutense de Madrid.

Madrid, Abril 1996

# **Agradecimientos**

En primer lugar quiero expresar mi agradecimiento a Dña. Milagros Fernández Centeno por la dedicación y entusiasmo que ha puesto en la elaboración de este trabajo de investigación, y por sus ánimos en los momentos más dificiles.

En segundo lugar, me gustaría mostrar mi agradecimiento a Don Julio Septién del Castillo y a Don Daniel Mozos Muñoz, por todas las horas que han pasado discutiendo distintos aspectos sobre la forma y contenido de este trabajo, así como por sus imprescindibles ánimos para conseguir la finalización del mismo.

Igualmente quiero agradecer a Don Román Hermida sus consejos e ideas, que me han permitido afianzar y explicar resultados de forma mucho más científica y clara.

También quiero agradecer a Don Francisco Tirado que contase conmigo para formar parte de su grupo de investigación, gracias a lo cual ha sido posible el desarrollo de este trabajo.

Tampoco puedo olvidar a Dña. Katzalin Olcoz Herrero, Don Victor Sánchez Canga y Don José Manuel Mendías Cuadros, que me han permitido discutir con ellos multitud de problemas e ideas, y han estado siempre dispuestos a darme ánimos y compañía.

Además, quiero agradecer a Don José Antonio López Orozco y Don Rafael Moreno Vozmediano las horas que han pasado ayudándome, para obtener los resultados sobre estimaciones de retardos presentados en este trabajo.

Por último, quiero dar las gracias a todos los demás miembros del Grupo de Arquitectura de Computadores del Departamento de Informática y Automática, por haberme escuchado y aconsejado siempre que lo he requerido.

Este trabajo ha sido posible gracias al Ministerio de Educación y Ciencia, por el soporte económico dado dentro del Plan de Becas de Formación de Personal Investigador, y gracias a la Comisión Interministerial de Ciencia y Tecnología, por las ayudas recibidas a través de los

proyectos CICYT TIC 92/0088 y CICYT TIC 94/0725-C03-02.

# Indice

| Resumen       |            |                                         |                             | ix |

|---------------|------------|-----------------------------------------|-----------------------------|----|

| 1. Síntesis d | le Alto Ni | el y Características Físicas            |                             | 1  |

| 1.1.          | Introdu    | ción                                    |                             | 1  |

| 1.2.          | Influenc   | as de las características físicas en la | s distintas fases de la SAN | 4  |

|               | 1.2.1.     | Compilación                             |                             | 8  |

|               | 1.2.2.     | Planificación de Operaciones            |                             | 9  |

|               |            | 1.2.2.1. Selección del tiempo de o      | ciclo                       | 10 |

|               |            | 1.2.2.2. Asignación de operacione       | es a pasos de control       | 11 |

|               | 1.2.3.     | Asignación del Hardware                 |                             | 13 |

|               |            | 1.2.3.1. Preasignación de Hardwa        | ге                          | 17 |

|               |            | 1.2.3.2. Asignación de instancias.      |                             | 18 |

|               |            | Algoritmos de tipo construc             | ctivo                       | 19 |

|               |            | Algoritmos de tipo iterativo            | )                           | 19 |

|               |            | Algoritmos iterativo-constr             | uctivo                      | 20 |

|               | 1.2.4.     | Diseño de la Unidad de Control          |                             | 20 |

|               | 1.2.5.     | Control del Proceso de Diseño           |                             | 21 |

| 1.3.          | Conexi     | n con herramientas de Diseño            |                             | 21 |

| 1.4.          | Conclus    | ones                                    |                             | 24 |

| 2. Técnicas   | de Estima  | ción de las Características Físicas     |                             | 29 |

| 2.1.          | Introduc   | ción                                    |                             | 29 |

| 2.2.          | Estimacio  | nes de área durante un proceso de S     | SAN                         | 31 |

|               | 2.2.1.     | Sistemas con minimización del cost      | te de multiplexores         | 32 |

|               |            | 2.2.1.1. Sistema Olympus                |                             | 32 |

|               |            | 2.2.1.2. Sistema Elf                    |                             | 34 |

|      |          | 2.2.1.3. Sistema HIS                                        | . 37 |

|------|----------|-------------------------------------------------------------|------|

|      | 2.2.2.   | Sistemas con minimización del número de interconexiones     | . 38 |

|      |          | 2.2.2.1. Sistema HAL                                        | . 38 |

|      |          | 2.2.2.2. Sistema PARTHENON                                  | 39   |

|      | 2.2.3.   | Sistemas con coste de interconexión fijo                    | . 41 |

|      |          | 2.2.3.1. Sistema Chippe                                     | . 41 |

|      |          | 2.2.3.2. Sistema de la Universidad de California, Berkeley  | . 42 |

|      |          | 2.2.3.3 Sistema SAW                                         | . 43 |

|      |          | 2.2.3.4. Sistema CHARM                                      | . 44 |

|      | 2.2.4.   | Sistemas con coste de interconexión obtenido por            |      |

|      | floorpl  | anning                                                      | . 45 |

|      |          | 2.2.4.1. BUD                                                | . 45 |

|      |          | 2.2.4.2. Sistema ADAM                                       | . 48 |

|      |          | 2.2.4.3. Sistema de la Universidad de Cleveland (Case       |      |

|      |          | Western Reserve University)                                 | . 50 |

|      | 2.2.5.   | Conclusiones sobre las estimaciones de los sistemas de SAN  | . 51 |

| 2.3. | Técnicas | s de Estimación de Bajo Nivel                               | . 52 |

|      | 2.3.1.   | Modelos teóricos                                            | . 54 |

|      |          | 2.3.1.1. PLEST                                              | . 54 |

|      |          | 2.3.1.2. LAST                                               | . 55 |

|      |          | 2.3.1.3. Sistema de la Universidad de California, San Diego | . 56 |

|      | 2.3.2.   | Modelos empíricos                                           | . 58 |

|      |          | 2.3.2.1. Modelo para Arrays de puertas en una dimensión     | . 58 |

|      |          | 2.3.2.2. Modelo para Arrays de Puertas en dos dimensiones   | . 59 |

|      | 2.3.3.   | Modelos procedurales                                        | . 59 |

|      |          | 2.3.3.1. Sistema de la Universidad de Yale (New Haven)      | 59   |

|      |          | 2.3.3.2. Sistema de la Universidad de Rutgers, New Jersey   | 61   |

|      |          | 2.3.3.3. Sistema de la Universidad de Kaiserslautern        | 62   |

|              |           | 2.3.3.4. Sistema de la Universidad de California, Berkeley   | 63  |

|--------------|-----------|--------------------------------------------------------------|-----|

|              |           | 2.3.3.5. Sistema de la Universidad de California, Irvine     | 65  |

|              | 2,3,4.    | Conclusiones de las estimaciones de SBN                      | 66  |

| 2.4.         | Conclus   | iones generales                                              | 68  |

| 3. El Sistem | a FIDIAS  | 5                                                            | 73  |

| 3.1.         | Estructur | a del Sistema FIDIAS                                         | 73  |

| 3.2.         | El Proces | so de Síntesis en FIDIAS                                     | 77  |

| 3.3.         | Subtarea  | de planificación-preasignación                               | 79  |

|              | 3.3.1.    | Selección del tiempo de ciclo                                | 80  |

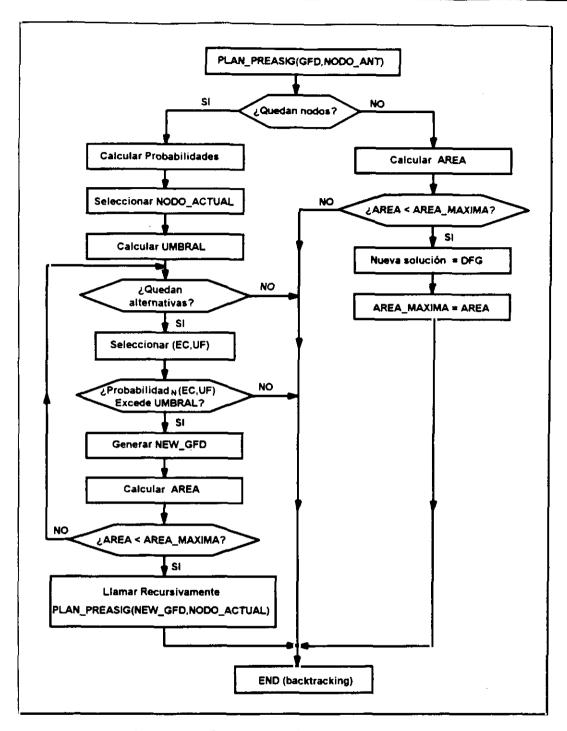

|              | 3.3.2.    | Planificación-Preasignación.                                 | 82  |

|              | 3.3.3.    | Evaluación del GFD planificado                               | 84  |

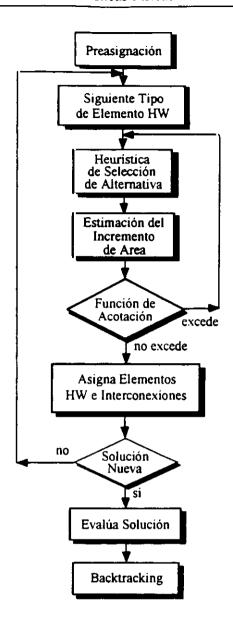

| 3.4.         | Subtarea  | de Asignación de Hardware                                    | 85  |

|              | 3.4.1.    | Técnicas de reducción del EDA                                | 87  |

|              | 3.4.2.    | Función de coste                                             | 87  |

|              |           | 3.4.2.1. Estimación de área                                  | 88  |

|              | 3.4.3.    | Heurísticas de Acotación                                     | 91  |

|              | 3.4.4.    | Heurísticas de guía                                          | 92  |

|              | 3.4.5.    | Medidas de testabilidad durante la asignación de hardware    | 92  |

|              | 3.4.6.    | Evaluación del diseño                                        | 93  |

| 3.5.         | Generac   | ión del control                                              | 94  |

| 3.6.         | Conclus   | iones                                                        | 94  |

|              |           | rea en SAN                                                   |     |

| 4.1.         | Introdu   | cción                                                        | 97  |

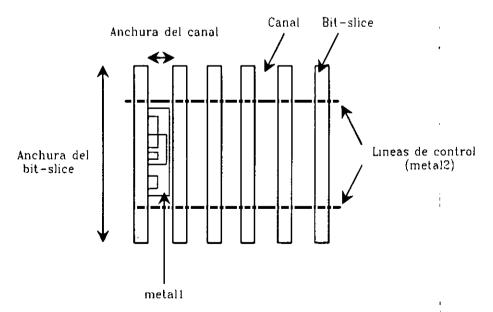

| 4.2.         | Conexio   | ón con una herramienta de SBN                                | 99  |

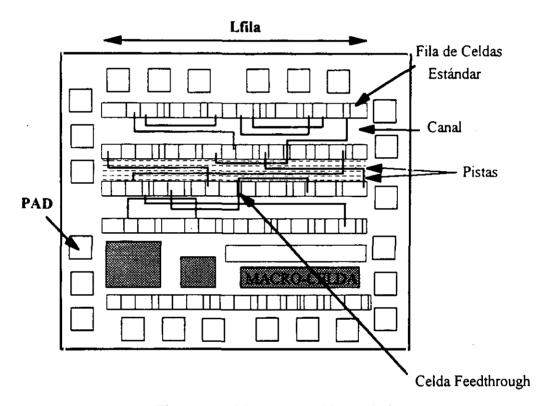

| 4.3.         | Caracte   | rísticas tecnológicas de un diseño con celdas estándar       | 102 |

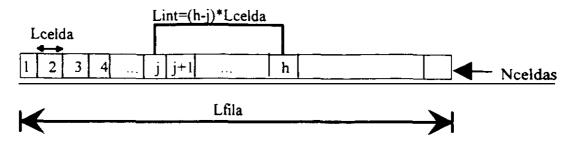

| 4.4.         | Modelo    | simple: Estimación de la longitud de una interconexión media | 104 |

| 4.5.         | Modelo    | refinado: Clasificación de las interconexiones               | 109 |

| 4.6.         | Nueva     | estimación de la longitud de una interconexión               | 114 |

|         | 4.7.         | Modelo completo: interconexiones multimódulo                           | 116 |

|---------|--------------|------------------------------------------------------------------------|-----|

|         | 4.8.         | Estimaciones finales para el modelo completo                           | 122 |

|         | 4.9.         | Estimaciones de la longitud de una interconexión durante el proceso de |     |

|         | diseñ        | o                                                                      | 125 |

|         |              | 4.9.1. Estimaciones después de la planificación-preasignación          | 125 |

|         |              | 4.9.2. Estimaciones durante y después de la asignación de hardware     | 126 |

|         |              | 4.9.3. Estimación del área del controlador                             | 129 |

|         | 4.10.        | Ejemplos                                                               | 130 |

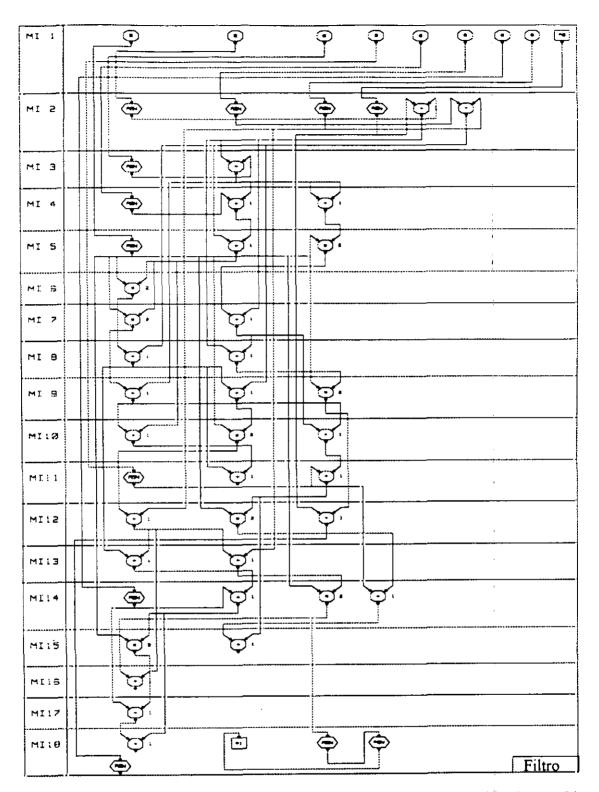

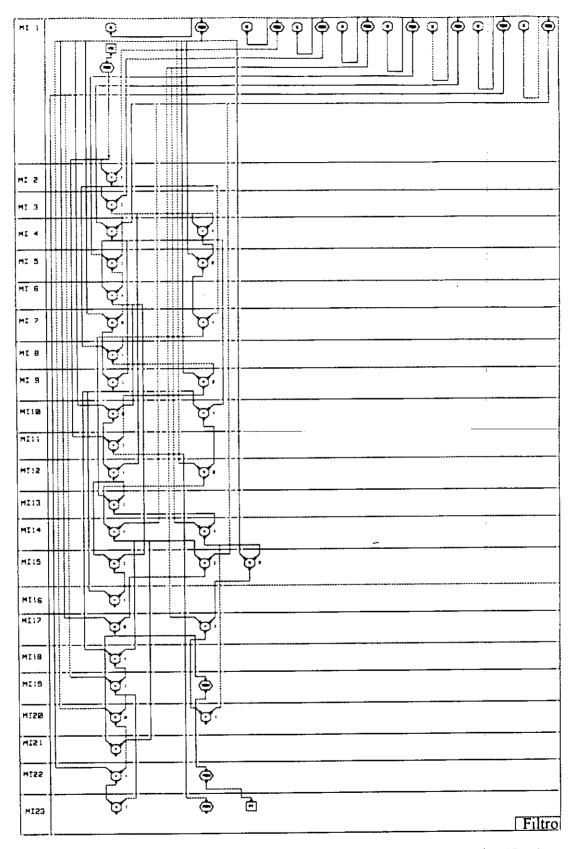

|         |              | 4.10.1. Filtro Elíptico de 5º Orden                                    | 131 |

|         |              | 4.10.2. Ecuación diferencial                                           | 132 |

|         |              | 4.10.3. Filtro-Ar                                                      | 133 |

|         | 4.11.        | Conclusiones                                                           | 134 |

| 5. Sele | cción        | del Ciclo de Reloj                                                     | 137 |

|         | <b>5</b> .1. | Introducción                                                           | 137 |

|         | 5.2.         | Trabajo Previo                                                         | 139 |

|         | 5.3.         | Minimización del tiempo de ejecución                                   | 142 |

|         |              | 5.3.1. Retardo de las operaciones del GFD                              | 143 |

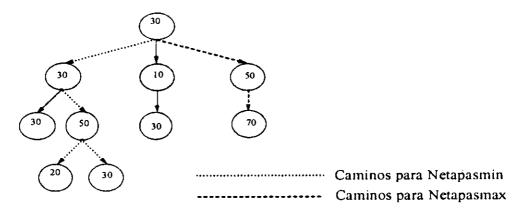

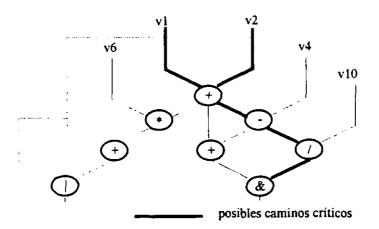

|         |              | 5.3.2. Búsqueda de los posibles caminos críticos                       | 146 |

|         |              | 5.3.2.1. Teoremas de selección de posibles caminos críticos            | 148 |

|         |              | 5.3.2.2. Algoritmo de Unificación de Caminos                           | 156 |

|         |              | 5.3.2.3. Algoritmo de búsqueda de posibles caminos críticos            | 161 |

|         |              | 5.3.2.4. Algoritmo modificado de búsqueda de caminos                   |     |

|         |              | criticos                                                               | 168 |

|         |              | 5.3.3. Obtención del tiempo de ejecución mínimo                        | 171 |

|         | 5.4.         | Minimización del área de la Unidad de control                          | 172 |

|         | 5.5.         | Algoritmo de Selección del tiempo de ciclo                             | 177 |

|         | 5.6.         | Ejemplos                                                               | 183 |

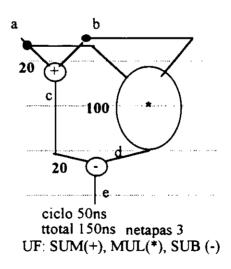

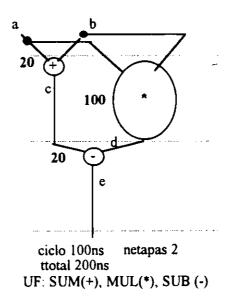

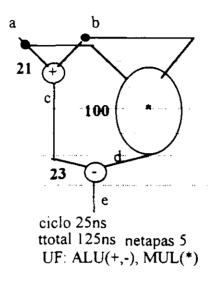

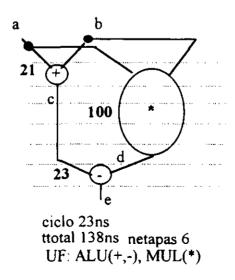

|         | ٠            | 5.6.1. FACET                                                           | 183 |

|               |           | B.3.2.1 Simulated annealing                                      | 255 |

|---------------|-----------|------------------------------------------------------------------|-----|

|               |           | B.3.2.2 Colocación dirigida por fuerzas                          | 256 |

|               |           | B.3.2.3 Particionamiento o algoritmo de min-cut                  | 257 |

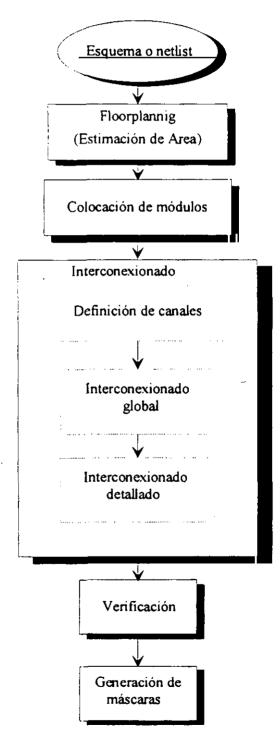

| B.4.          | Intercon  | exionado                                                         | 257 |

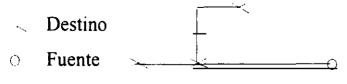

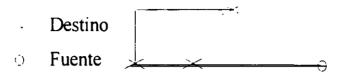

|               | B.4.1     | Interconexionado global                                          | 258 |

|               | B.4.2     | Interconexionado detallado                                       | 259 |

|               | B.4.3     | Interconexionado de alimentación y tierra                        | 260 |

| <b>B</b> .5.  | Reglas d  | e diseño                                                         | 261 |

| <b>B</b> .6.  | Lengua    | e EDIF                                                           | 261 |

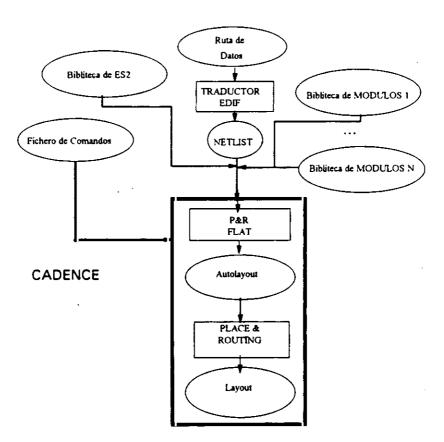

| C. Conversi   | ón de FII | DIAS a CADENCE                                                   | 265 |

| <b>C</b> . 1. | De la es  | tructura RTL al layout                                           | 265 |

| C. 2.         | La ruta   | de Datos                                                         | 266 |

| C. 3.         | Generac   | ión del fichero EDIF                                             | 270 |

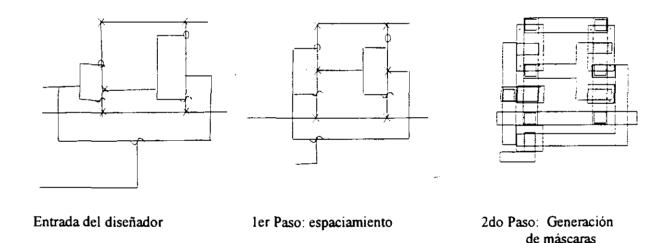

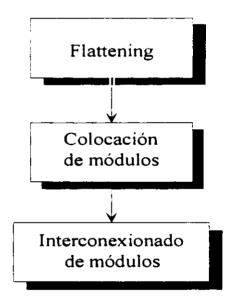

| C.4.          | Generaci  | ón automática del layout                                         | 271 |

|               | C.4.1     | Generación del diagrama de flujo                                 | 273 |

|               | C.4.2     | Definición de la función para el paso Flattening                 | 275 |

|               | C.4.3     | Definición de la función para el paso de colocación de           |     |

|               | módul     | os                                                               | 277 |

|               |           | C.4.3.1 . Comandos de definición de prioridades de las redes     | 277 |

|               |           | C.4.3.2. Inicialización del algoritmo de colocación de módulos   | 277 |

|               |           | C.4.3.3. Definición de la malla para realizar la colocación      | 279 |

|               |           | C.4.3.4. Colocación de celdas de entrada/salida                  | 280 |

|               |           | C.4.3.5. Colocación de celdas estándar                           | 280 |

|               |           | C.4.3.6. Adición de las celdas esquinas                          | 281 |

|               |           | C.4.3.7. Fase de justificación                                   | 282 |

|               |           | C.4.3.8. Adición de celdas terminales a cada una de las filas de |     |

|               |           | celdas                                                           | 283 |

|               |           | C.4.3.9. Salvar el diseño                                        | 284 |

Indice

|              | C.4.4 | C.4.4 Definición de la función para el paso de interconexionado |                            | 284 |

|--------------|-------|-----------------------------------------------------------------|----------------------------|-----|

|              |       | C.4.4.1.                                                        | Generación de canales      | 284 |

|              |       | C.4.4.2.                                                        | Interconexionado global    | 285 |

|              |       | C.4.4.3.                                                        | Interconexionado detallado | 285 |

|              |       | C.4.4.4.                                                        | Salvar el diseño           | 286 |

| Bibliografia |       |                                                                 |                            | 289 |

# Resumen

El objetivo principal de este trabajo de investigación es estudiar las influencias de las características físicas del CI sobre el área y retardo de los diseños obtenidos en un proceso de Síntesis de Alto Nivel, y diseñar técnicas de estimación de dichas características, rápidas, precisas y fieles, para todas las fases de dicho proceso.

El primer problema abordado, es la elaboración de una función para medir la calidad de los diseños obtenidos durante la asignación de hardware en un proceso de Síntesis de Alto Nivel. Esta función debe ser una aproximación al área real del circuito, que a su vez es la suma del área de los módulos y de las interconexiones. Éstas áreas dependen de la tecnología que se esté utilizando, de la colocación de los módulos en el circuito final, y de cómo se realice el interconexionado de éstos (tanto de las interconexiones internas de los módulos como de las externas). Por tanto, depende de las características físicas del CI y de las herramientas y tecnologías de diseño, y es necesario estimarlas. En todos los casos las estimaciones se necesitan realizar muchas veces durante un proceso de síntesis, y por tanto deben ser muy rápidas. Además deben ser lo suficientemente fieles para dirigir correctamente el proceso de asignación de hardware.

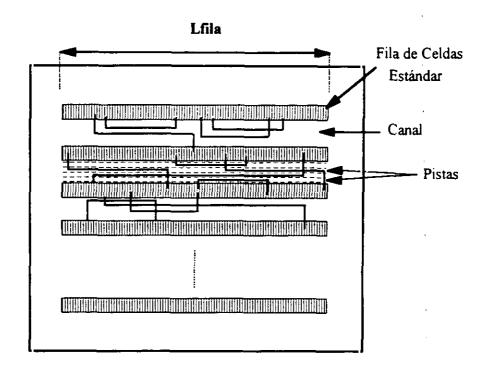

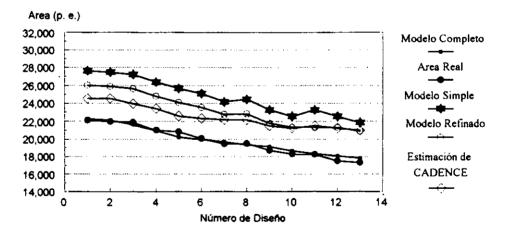

En este trabajo se presenta un método de estimación de área que puede utilizarse durante las distintas fases de la síntesis, como en la preasignación y en la asignación de hardware, y en la generación del hardware de control, y que es lo suficientemente rápido y fiel para dirigir el proceso de diseño correctamente, sin incrementar la complejidad de éste. Como las influencias de las características físicas en el área del circuito, dependen de la tecnología de diseño utilizada, y el estudio para todas ellas es un trabajo de una extensión excesiva, se particulariza el estudio para celdas estándar. Sin embargo, muchas de las ideas propuestas pueden utilizarse para macroceldas y arrays de puertas.

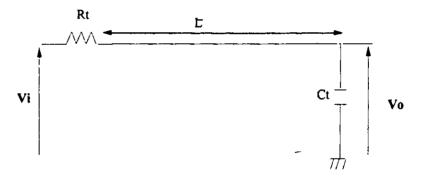

El segundo problema que se trata en este trabajo es la obtención de circuitos con un funcionamiento eléctrico correcto. Para este fin, es necesario considerar los retardos de los módulos e interconexiones, que a su vez dependen de la tecnología utilizada y de los algoritmos de colocación e interconexionado de módulos. El retardo del interconexionado es un dato que no se conoce hasta que no se ha generado el layout, y por tanto es necesario estimarlo.

En este trabajo se presenta un algoritmo de selección del tiempo de ciclo que tiene en cuenta la biblioteca de módulos disponible, con información sobre los retardos de los módulos, y el retardo de las interconexiones, mediante estimaciones que consideran la tecnología utilizada y la forma de trabajo de los algoritmos de colocación e interconexionado de módulos. De esta forma, se asegura que los circuitos generados tienen un comportamiento eléctrico correcto. Además, para conseguir tiempos de ciclo óptimos, que permitan cumplir los objetivos del usuario en cuanto al área y tiempo de ejecución del circuito, se realiza un estudio global de la especificación dada y de la biblioteca de módulos.

La memoria que se presenta se divide en seis capítulos y tres apéndices. En el capítulo 1 se realiza una introducción a la Síntesis de Alto Nivel y se plantea la necesidad de realizar estimaciones de las características físicas del circuito para dirigir correctamente el proceso de diseño.

En el capítulo 2 se exponen los principales sistemas de Síntesis de Alto Nivel que realizan algún tipo de estimación del área de interconexionado, así como sus ventajas y sus inconvenientes, y la necesidad de realizar nuevas estimaciones más precisas. A continuación se presentan algunos métodos de estimación de área de circuitos integrados bastante precisos, pero muy lentos para incorporarlos dentro de una herramienta de Síntesis de Alto Nivel.

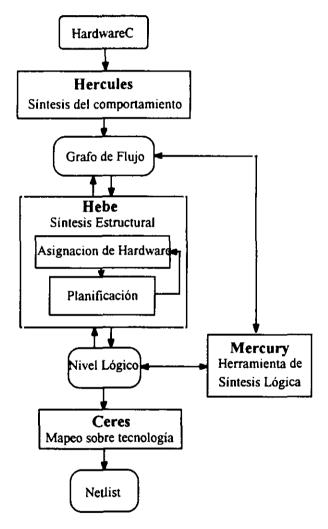

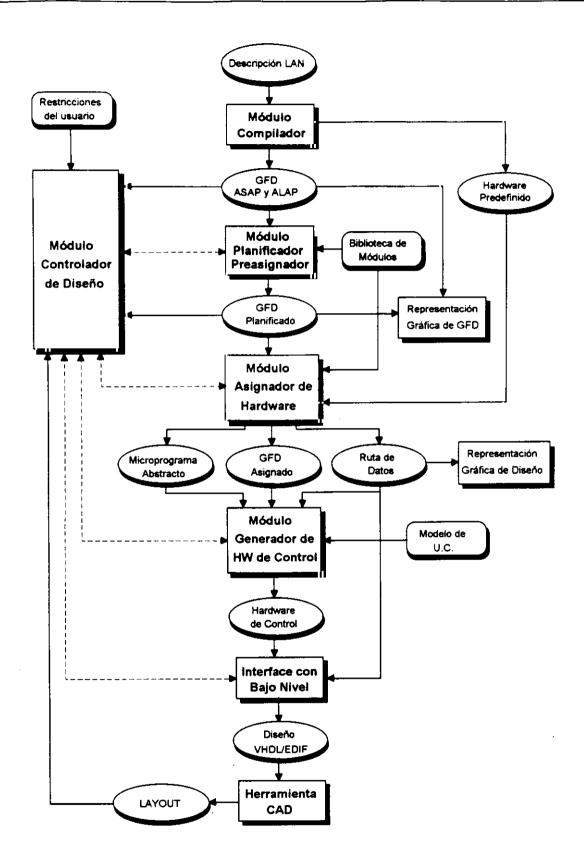

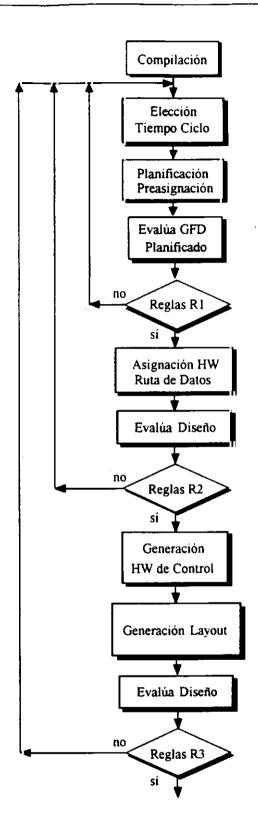

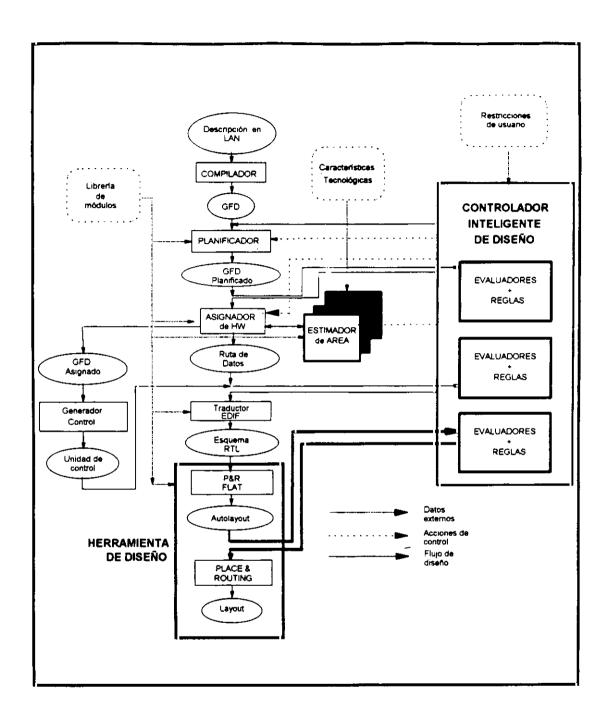

El capítulo 3 se centra en el sistema FIDIAS, que es un sistema de Síntesis de Alto Nivel dentro del cual se integra este trabajo de investigación. Se muestra que también en este sistema es necesario realizar estimaciones, y cómo y dónde se deben integrar éstas.

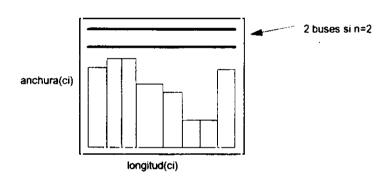

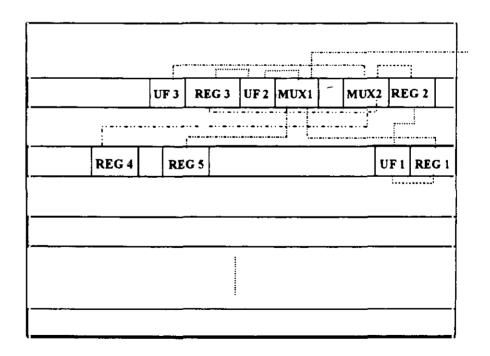

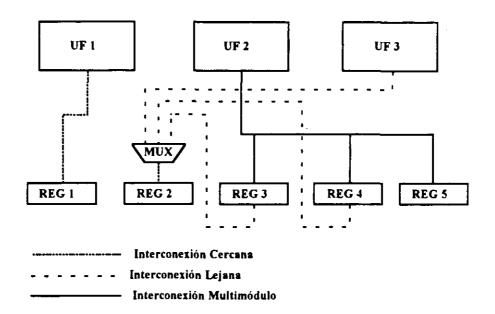

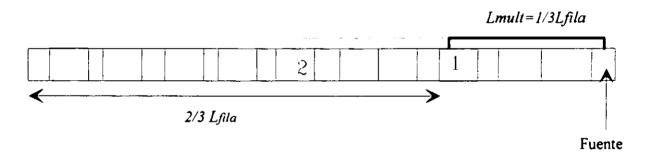

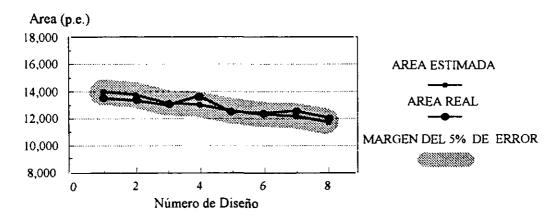

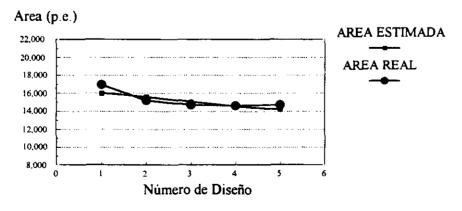

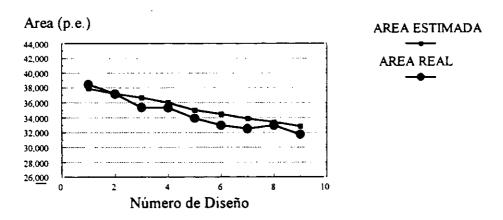

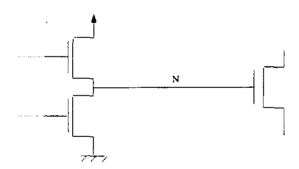

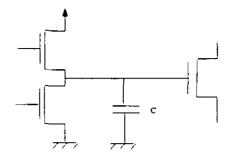

En el capítulo 4 se realiza un estudio de la metodología de trabajo de las herramientas de CAD, y de las características físicas de los circuitos integrados. Se han clasificado las interconexiones en función del número de módulos que conectan. Para cada uno de los tipos se ha obtenido una estimación de su longitud. Las interconexiones que hemos denominado cercanas tienen longitud constante. Para las lejanas y multimódulo se ha obtenido una fórmula en función del número total de interconexiones de cada tipo y del área de celdas estándar del diseño, datos conocidos cuando se ha terminado la generación de un diseño. Este método de estimación de la longitud de las interconexiones nos permite conocer el área de los módulos, siempre que en la biblioteca se disponga de información sobre el número y tipo de interconexiones que contiene cada uno de ellos. Las estimaciones se han integrado en el sistema FIDIAS y, mediante varios ejemplos, se ha demostrado la fidelidad y precisión de estas estimaciones de área, que en todos los casos tienen un error inferior al 5%.

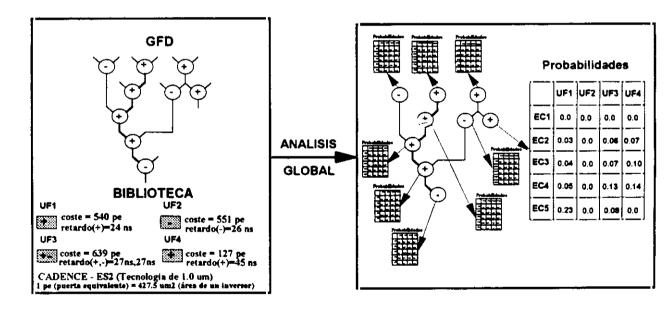

En el capítulo 5 se presenta un algoritmo de selección del tiempo de ciclo, que tiene en cuenta la biblioteca de módulos, las restricciones del usuario y que estudia de forma global el GFD. El algoritmo de selección realiza una búsqueda de los caminos que para algún tiempo de ciclo pudieran ser críticos, puesto que son los únicos que influyen en el tiempo de ejecución del algoritmo. Sobre las operaciones situadas en estos caminos, se realiza la selección del tiempo de ciclo, permitiendo más de una Unidad Funcional para implementar cada operación, y mediante unos parámetros que miden los objetivos del usuario, en cuanto a la minimización del área y tiempo del circuito. De esta forma, el tiempo de ciclo utilizado para realizar la planificación depende de cada diseño y objetivos en particular, con lo cuál los resultados obtenidos se ajustan más a las necesidades del usuario.

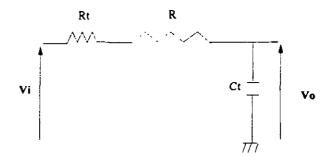

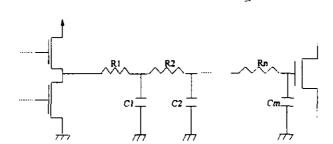

Por último, en el capítulo 6, y a partir de las estimaciones del área de las interconexiones del capítulo 4, se presenta la forma de calcular el retardo de éstas. Se realiza un estudio completo sobre el retardo del interconexionado, obteniendo un modelo físico para una interconexión, y a partir de éste se calcula el retardo, utilizando el método del polo dominante. Además, se presenta el método para incluir los retardos de las interconexiones en el cálculo del tiempo de

ciclo, con el objetivo de obtener diseños con un funcionamiento eléctrico correcto.

Todos los resultados del capítulo 4 se basan, por una parte en la forma de trabajo de las herramientas de Síntesis de Bajo Nivel, y por otra parte en la tecnología utilizada. En el apéndice A se puede encontrar un estudio detallado sobre las distintas tecnologías de generación de Circuitos Integrados, y en el apéndice B se presentan los distintos algoritmos de colocación e interconexionado de módulos, cuyo conocimiento es necesario para entender los resultados de este trabajo.

Finalmente, en el apéndice C se explica la conexión de nuestra herramienta de Síntesis de Alto Nivel con una herramienta de Síntesis de Bajo Nivel, gracias a la cual se han podido realizar un gran número de experimentos, con los cuáles dirigir y validar la calidad de nuestras estimaciones.

# Capítulo 1.

# Síntesis de Alto Nivel y Características Físicas

# 1.1. Introducción

En la última década la tecnología de diseño de Circuitos Integrados (CIs) se ha desarrollado de forma espectacular, con la generación de múltiples herramientas de Diseño Asistido por Computador (CAD) para desarrollo de CIs y diseño lógico. Este desarrollo fundamentalmente es una consecuencia de dos factores:

- El gran avance de las tecnologías de fabricación de circuitos VLSI, que ha permitido incrementar de forma espectacular la densidad de encapsulamiento, elevando enormemente la complejidad de los diseños. Actualmente muchos diseños incorporan arquitecturas completas en un único chip.

- La necesidad de producir diseños en el menor tiempo posible y con el menor número de errores. Por tanto, se requiere utilizar herramientas para acelerar el proceso de diseño y verificación.

Dadas las consideraciones anteriores, se puede concluir que el nivel lógico no es un nivel natural para el diseñador de circuitos complejos. Es prácticamente inconcebible describir un sistema complejo en términos de expresiones booleanas. Además, la utilización cada vez mayor de ASICs (Circuitos Integrados de Aplicación Específica) en múltiples áreas de aplicación, implica el acceso a esta tecnología de usuarios con poca o ninguna experiencia en el diseño de CIs. Estos factores generan la necesidad de utilizar herramientas para automatizar el diseño de circuitos desde un nivel de abstracción más elevado, con el fin de ahorrar tiempo

y dinero, y permitir el acceso a las ventajas de la nueva tecnología a mayor número de usuarios, no necesariamente expertos.

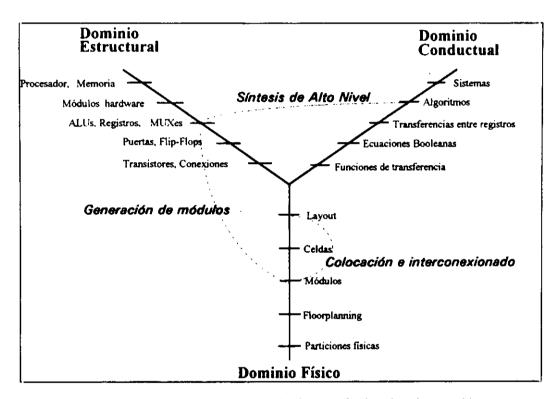

Los posibles dominios de descripción de un diseño y sus niveles de abstracción respectivos han sido representados por Gajski [GaKu83] mediante un diagrama en forma de Y similar al de la figura 1.1. Cada uno de los tres ejes representa uno de los dominios: el conductual, el estructural, y el físico. En cada dominio, la descripción puede realizarse a distintos niveles, de mayor grado de abstracción cuanto más alejados se encuentren del origen.

Figura 1.1 Dominios de Descripción y Niveles de Abstracción

En el dominio conductual el circuito se describe mediante una serie de relaciones entre las entradas y las salidas del mismo. En el dominio estructural se especifican los componentes y las interconexiones entre ellos. En el dominio físico se describen los módulos reales que integran el circuito y su distribución espacial.

En la figura 1.1 también se representan un conjunto de transformaciones entre distintos niveles de los diferentes dominios, que pueden constituir un proceso de diseño. Entre todos los

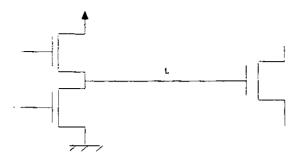

posibles puntos de partida y llegada dentro del desarrollo de CIs, la "Síntesis de Alto Nivel" (SAN) [GaRa94] parte de una descripción algorítmica del comportamiento del circuito. y obtiene automáticamente la estructura del sistema a nivel de transferencia de registros (RTL). La finalización del diseño se conseguiría mediante la generación de los módulos del nivel RTL, seguido de un proceso de colocación e interconexionado de éstos para generar el layout final (Apéndice B). Estos procesos suelen realizarse mediante la utilización de herramientas comerciales de CAD.

A continuación vamos a centrarnos en el proceso de SAN. El punto de partida, es decir, la descripción del comportamiento del circuito, debe realizarse en un lenguaje de alto nivel (LAN). Para facilitar la conexión con otras herramientas que trabajan en otros dominios descriptivos y/o niveles de abstracción, se pueden utilizar lenguajes estándar de descripción de hardware (LDH). Entre todos los LDH disponibles, uno de los más aceptados es VHDL. Además, el diseñador puede introducir un conjunto de restricciones y objetivos, básicamente de coste y velocidad del diseño, y el resultado proporcionado por la herramienta debe respetarlas.

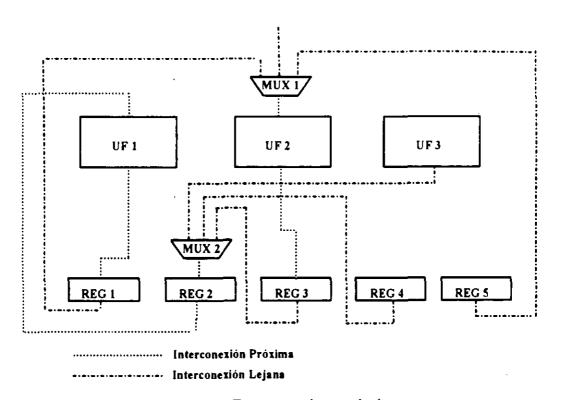

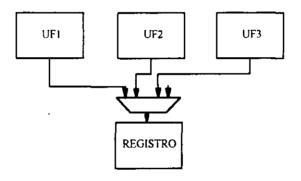

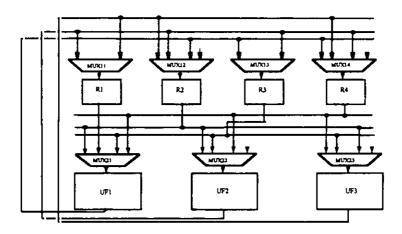

Por otra parte, en su punto de llegada, el nivel RTL del dominio estructural, se especifican las unidades funcionales (sumadores-restadores, multiplicadores, comparadores, etc.), las unidades de almacenamiento (registros, memorias), y las interconexiones (buses, multiplexores) que componen el diseño, así como la secuencia de control, a partir de algún modelo de unidad de control dado.

Entre las ventajas aportadas por la Síntesis de Alto Nivel [McPC88] no sólo está la disminución del coste de los circuitos debido a la reducción del tiempo de diseño, sino también:

Reducción del número de errores: Si se puede verificar que el proceso de SAN es correcto, podrá asegurarse la corrección por construcción del diseño obtenido. Esto permitirá reducir la probabilidad de aparición de errores y, por consiguiente, el tiempo invertido en la depuración de los mismos.

- Posibilidad de explorar el espacio de diseño: Una buena herramienta de SAN

deberá ser capaz de producir diferentes diseños, de distintos estilos, para una misma

especificación de partida, siempre dentro del conjunto de restricciones establecido

por el diseñador.

- Posibilidad de auto-documentación: El sistema de síntesis puede dejar constancia de cada una de las decisiones de diseño, y de los motivos que le indujeron a adoptarla.

- Acceso de mayor número de usuarios a la tecnología VLSI: La automatización

del proceso de diseño se efectuará desde un nivel de abstracción mayor que los

disponibles en las herramientas, y esto permitirá diseñar sus propios CIs a usuarios

no necesariamente familiarizados con sus características de más bajo nivel.

# 1.2. Influencias de las características físicas en las distintas fases de la SAN

De las consideraciones realizadas en el apartado anterior se puede deducir que la SAN es una etapa automática dentro del proceso global de diseño del CI. Sin embargo no puede tratarse como una fase aislada del resto. Los estudios realizados por McFarland y Kowalski [McKo90] sobre las influencias de factores del nivel físico en los resultados finales, nos muestran que, incluso en las decisiones que se toman en las primeras etapas de diseño, es necesario tener en cuenta las características físicas de los módulos, tanto del área como del retardo.

En el Apéndice A se presenta un estudio de los diferentes estilos de diseño VLSI que existen hoy en día. Observando las características de cada uno de ellos, puede sacarse como conclusión que los resultados obtenidos para un mismo diseño utilizando diferentes estilos, difieren totalmente tanto en coste final como en rendimiento. Por tanto, durante la SAN es

crucial tener en cuenta el estilo de diseño que se va a utilizar. Al mismo tiempo, los resultados obtenidos por distintas herramientas CAD pueden modificar los resultados, dependiendo del tipo de algoritmos que utilicen para realizar la colocación de los módulos y su interconexionado [MSHO92].

Por consiguiente, para que la síntesis del circuito integrado esté debidamente optimizada es necesario que durante todo el proceso de síntesis se tengan en cuenta:

- Las características físicas de la tecnología y de los módulos particulares que se van a utilizar.

- Las herramientas y estilo de diseño que se van a emplear para realizar la colocación e interconexionado de dichos módulos

El tema principal de este proyecto es el estudio de las mutuas influencias entre las características físicas de los CIs, las herramientas CAD con que se diseñan y los algoritmos de SAN.

Debido a la complejidad de estas mutuas influencias y, por tanto, de la necesidad de generar una enorme cantidad de experimentos para obtener conclusiones sobre su comportamiento, para una herramienta y un estilo de diseño en particular, existen muy pocos sistemas en la literatura que hayan realizado investigaciones relativas a este tema.

Aunque para cada estilo de diseño pueden existir diferentes tecnologías, cada una de ellas incluye todas las reglas para un estilo de diseño en particular. Por lo tanto, a partir de ahora utilizaremos la palabra tecnología para referirnos a un estilo de diseño y tecnología particulares.

Las características tecnológicas se conocen a priori, y pueden realizarse medidas sobre su influencia en el área y retardo de los módulos. Sin embargo, la colocación e interconexionado de los módulos no se conoce hasta que no se ha generado el layout final del circuito. Para obtener información sobre dicha colocación e interconexionado es interesante realizar la

conexión de la herramienta de SAN con la herramienta de CAD que va a generarlos. De esta forma, es posible experimentar y obtener el suficiente número de diseños para sacar conclusiones sobre la metodología de trabajo de los algoritmos de colocación e interconexionado de módulos y, a partir de ellas, realizar estimaciones sobre las influencias de las características fisicas del circuito integrado y utilizarlas en las decisiones que se toman en SAN.

Además, la conexión de la herramienta de SAN con la herramienta de CAD permitirá comprobar si dichas estimaciones son correctas. La realización de estos experimentos es sólo posible si se automatiza en gran parte las interacciones con la herramienta de CAD, porque la interacción manual con el proceso incrementa enormemente el tiempo de diseño.

Como la SAN consta de un grupo de tareas con diferentes funciones, las estimaciones de las características físicas del CI hay que realizarlas para cada una de estas tareas. Seguidamente vamos a presentar las diferentes etapas de la SAN y las estimaciones necesarias en cada una de ellas.

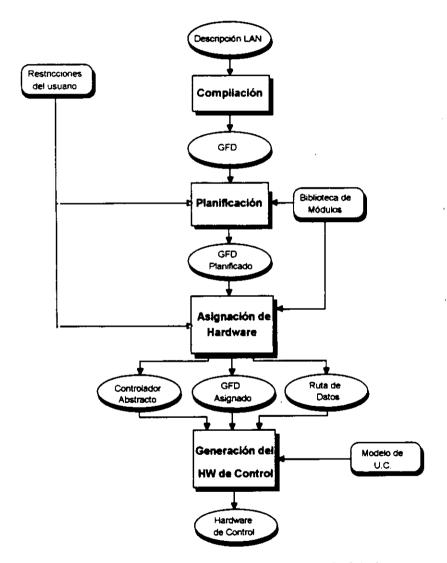

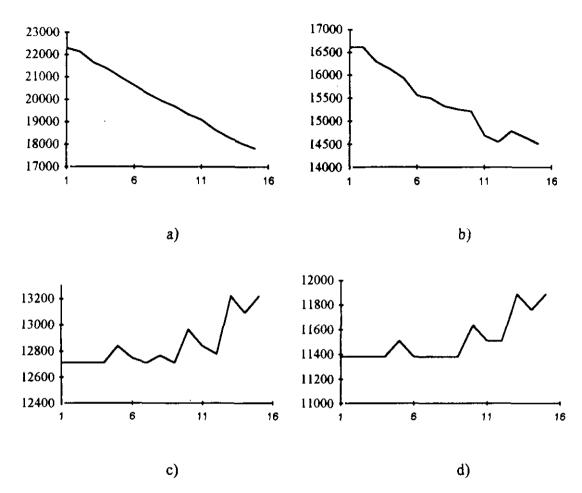

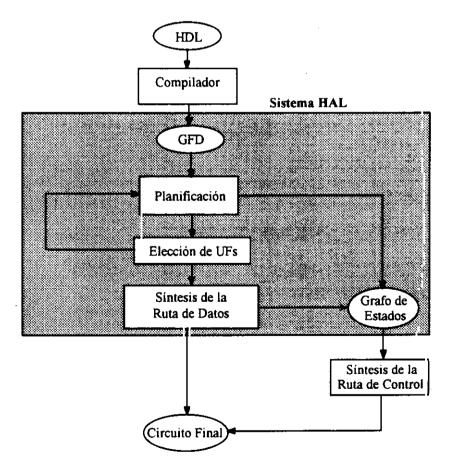

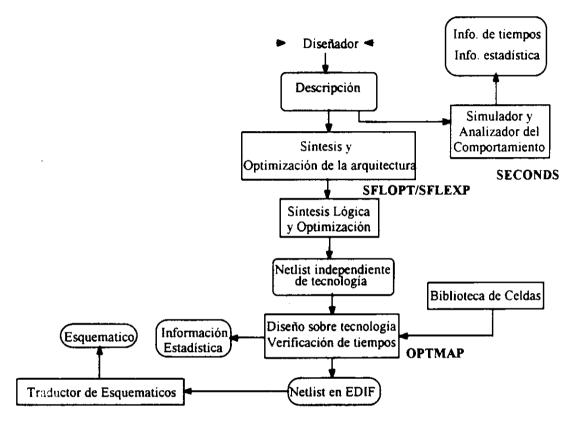

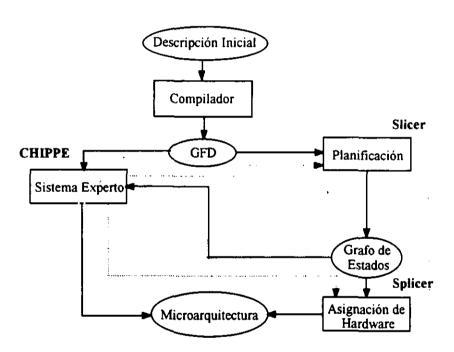

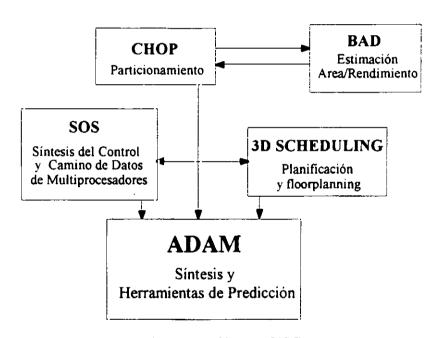

En la figura 1.2 se muestra un esquema de un proceso de SAN. Podemos distinguir 4 tareas fundamentales:

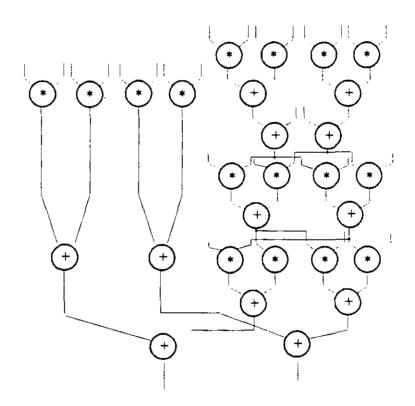

- 1.- Compilación. La primera fase necesaria en cualquier proceso de SAN, es la traducción de la descripción inicial, que como hemos dicho viene expresada en un LAN, a una representación intermedia más fácil de manejar por el resto de los módulos del sistema. Normalmente la representación elegida es un grafo de flujo de datos (GFD) y control, en el cual los nodos representan las operaciones a realizar, y las aristas el flujo de los datos. Esta fase es la que se denomina compilación, que, además, es la encargada de analizar la descripción de partida y de realizar sobre ella un conjunto de transformaciones orientadas a su optimización.

- 2 y 3 Planificación y Asignación de Hardware. Después de la compilación, la mayoría de las herramientas de SAN existentes distinguen dos subtareas que están muy

interrelacionadas entre sí: la planificación de operaciones y la asignación de hardware.

La primera de estas dos subtareas se encarga de la ubicación temporal, es decir, de asignar las operaciones a "pasos de control". Un paso de control es el equivalente a un ciclo de reloj.

Figura 1.2 Tareas de un proceso de SAN

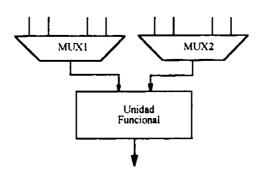

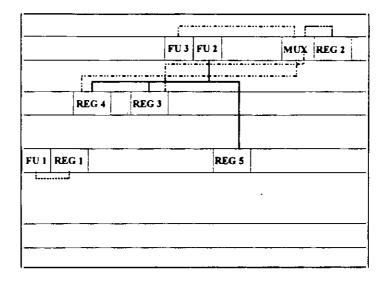

La otra subtarea, la asignación de hardware, decide qué elemento hardware va a realizar cada operación, dónde se almacenará el resultado y los caminos de interconexionado necesarios. El módulo asignador recibe como entrada una biblioteca de módulos, donde están almacenadas las Unidades Funcionales (UFs) disponibles para realizar las operaciones. El resultado de esta tarea es una ruta de datos, es decir, un conjunto de módulos conectados entre sí.

Esta división en dos subtareas es una consecuencia de que el proceso de síntesis consiste en una doble asignación de las operaciones incluidas en la descripción del comportamiento, a pasos de control y a módulos hardware. La complejidad de tratar estos dos problemas de una forma global es muy grande y por eso, aunque actualmente esta tendencia está cambiando, muchos de los sistemas no abordan la interdependencia existente entre ellos, y tratan cada una de estas tareas por separado. Aún así, cada una de ellas es un problema NP completo.

En una gran parte de los sistemas la planificación es una fase previa a la asignación de hardware, puesto que no es posible decidir qué UF puede realizar una operación si no se sabe de cuanto tiempo se dispone para realizarla. Sin embargo, en sistemas como Cathedral [DCGM90] esto no ocurre así. Primero se decide cuál es el mínimo hardware necesario para realizar todas las operaciones en el tiempo impuesto por el usuario, y luego se realiza la planificación en función de dicho hardware. En la actualidad, la mayoría de los planificadores deciden al menos qué tipo de UF va a realizar cada operación; es lo que se denomina preasignación de hardware o asignación de tipos. En este caso el asignador de hardware decide qué instancia en concreto realizará la operación (asignación de instancias).

4.- Generación de control. La última tarea de la SAN es la generación del control, que tiene como función la generación de la unidad de control, basándose en la planificación y asignación de hardware realizadas anteriormente.

En los apartados sucesivos vamos a explicar más detenidamente cada una de estas tareas, y las influencias de las características físicas del circuito integrado sobre cada una de ellas.

# 1.2.1. Compilación

La primera decisión a la hora de implementar un sistema de SAN es la selección del LAN

empleado para la descripción de partida. En los primeros sistemas de SAN, los lenguajes solían ser estándares de tipo procedural (como Pascal o C modificados para detallar algunos aspectos específicos del hardware). Sin embargo, la posibilidad de utilizar lenguajes estándares capaces de servir para la descripción de hardware en cualquiera de los niveles de varios dominios diferentes, así como de simular las descripciones, ha llevado a la mayoría de las herramientas de SAN a la utilización de VHDL como lenguaje de descripción del comportamiento de partida. Esto permite además, la simulación de dicha descripción a nivel de comportamiento, para asegurar que es correcta. Este lenguaje tiene un extenso soporte comercial y permite construcciones condicionales, lazos, procedimientos, funciones y asignaciones concurrentes y secuenciales.

El compilador también es el encargado de realizar transformaciones de alto nivel que tratan de optimizar la representación interna. Estas transformaciones pueden ser la eliminación de código muerto, extracción de código invariante de los bucles, etc.

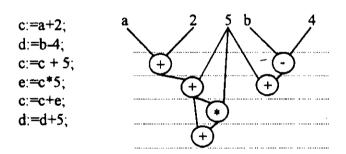

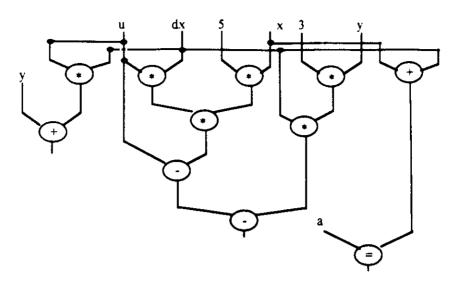

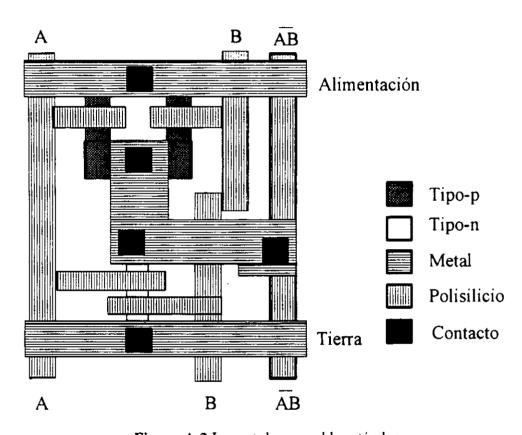

Figura 1.3 Ejemplo de GFD

En la figura 1.3 presentamos un ejemplo con un fragmento de una descripción de un circuito y el GFD correspondiente.

# 1.2.2. Planificación de Operaciones

Esta segunda tarea es, junto con la asignación de hardware, uno de los problemas clave de la SAN. Consiste en la distribución temporal de las operaciones del GFD, a partir de unas restricciones de área y tiempo dadas por el usuario, con un objetivo principal: obtener una

carga de trabajo equilibrada entre los distintos pasos de control, que permita el máximo aprovechamiento del hardware. El número total de pasos de control del algoritmo es lo que determinará la longitud de la memoria de la Unidad de Control -en el caso de un control microprogramado-, o el número de estados -para un control construido por una máquina de estados-. Por lo tanto, otro objetivo a minimizar por el planificador debe ser el número total de pasos de control del diseño final. Dentro de la planificación se pueden distinguir dos subtareas: la selección del tiempo de ciclo y la asignación de operaciones a pasos de control, que vamos a estudiar por separado a continuación.

#### 1.2.2.1. Selección del tiempo de ciclo

Para realizar una planificación es necesario seleccionar el tiempo de ciclo que se va a utilizar en el diseño. Como veremos posteriormente, éste es uno de los factores que más van a influir en la obtención de la planificación óptima. En su selección hay que tener en cuenta los tiempos muertos de los operadores, es decir, el tiempo que transcurre desde que acaba de realizarse una operación hasta que se termina el tiempo de ciclo. Un tiempo de ciclo pequeño, en general, conduce a planificaciones donde los tiempos muertos de los operadores son pequeños, y por lo tanto, los tiempos de ejecución son menores. Sin embargo, el número de pasos de control aumenta al disminuir el tiempo de ciclo, puesto que se incrementa el número de etapas necesarias para realizar cada una de las operaciones. El incremento en el número de pasos de control produce a su vez un incremento en el área de la Unidad de Control.

Los tiempos muertos de los operadores para un determinado tiempo de ciclo dependen de los retardos de las UFs que los implementan. Por lo tanto es necesario tener en cuenta las UFs disponibles en la biblioteca en dicha selección.

Otro factor importante, que depende de la colocación de los módulos y de sus interconexiones en el layout final, es el retardo debido al interconexionado. Si éste no se tiene en cuenta, puede ocurrir que no se disponga de tiempo suficiente para la transmisión de todas las señales en un paso de control, lo cual conduciría a un mal funcionamiento del circuito. El **retardo de una**

interconexión depende, entre otros factores, de la tecnología que se vaya a utilizar, y de la longitud de dicha interconexión, desconocida hasta la generación del layout, y que será necesario estimar. Por lo tanto, en la selección del tiempo de ciclo, se deben tener en cuenta la biblioteca de módulos disponible, los retardos del interconexionado, y las restricciones del usuario en cuanto al área y tiempo de ejecución del circuito.

En la mayoría de los sistemas de SAN, la selección del tiempo de ciclo la realiza el diseñador, o se hace con un valor fijo. Esto puede dar lugar a diseños no óptimos, e incluso a diseños con una simulación eléctrica incorrecta, sobre todo si no se tiene en cuenta el retardo de las interconexiones.

En este trabajo presentaremos un método de selección del tiempo de ciclo y de estimación del retardo de interconexionado, que, además de permitir obtener planificaciones con tiempos de ejecución bastante aceptables, asegura el buen funcionamiento del circuito.

#### 1.2.2.2. Asignación de operaciones a pasos de control

Una vez seleccionado el tiempo de ciclo el planificador debe asignar las operaciones a pasos de control tratando de minimizar su número. Podemos distinguir dos tipos de planificaciones:

- Si el número de módulos hardware de cada tipo (UFs y registros) ya se conoce antes

de realizar la planificación, el planificador debe tratar de minimizar el número de

pasos de control a partir de dicho hardware. Este tipo de planificaciones se presenta

en sistemas donde el usuario restringe mucho el hardware disponible o en sistemas

donde se realiza una preasignación de hardware antes de realizar la planificación.

- Si el número de módulos de cada tipo no es una restricción al planificador, también deberá equilibrar el paralelismo para poder realizar la implementación con el mínimo hardware posible, mediante la reutilización de UFs y registros en varios pasos de

control. En algunas planificaciones de este tipo, también se realiza simultáneamente una preasignación de hardware, es decir, se decide qué tipo de módulo va a realizar cada una de las operaciones.

En esta fase es necesario conocer el retardo de los módulos que van a realizar las operaciones, para estimar el número de pasos de control mínimo para cada operación.

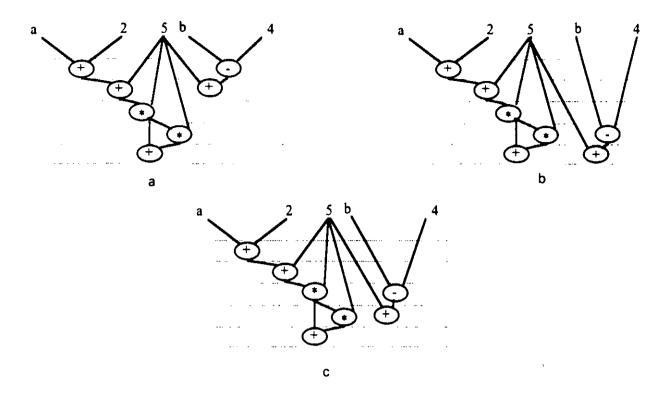

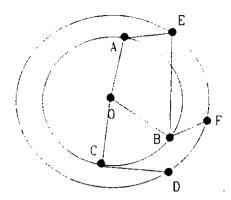

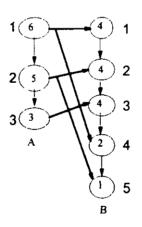

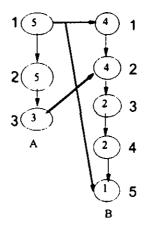

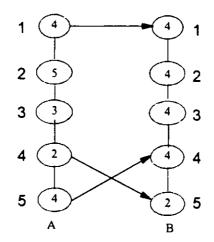

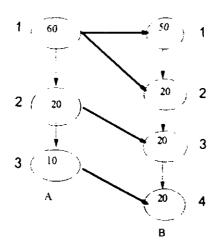

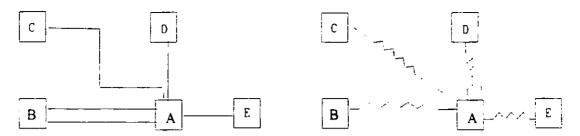

Existen dos tipos de planificaciones muy fáciles de generar, si se asume un tiempo determinado de ejecución para cada operación, que proporcionan el mínimo número de etapas para ejecutar el algoritmo. Son las planificaciones ASAP ("As Soon As Possible") y ALAP ("As Late As Possible"). La planificación ASAP coloca cada nodo del GFD en la primera etapa donde pueda realizarse (cuando todos los operandos que necesita están disponibles). Un ejemplo se muestra en la figura 1.4a, donde se ha asumido que cada operación puede ejecutarse en una etapa de control. Por el contrario, la planificación ALAP coloca cada nodo en la última etapa donde pueda realizarse, sin incrementar el número de etapas dado por la planificación ASAP. La figura 1.4b nos muestra la planificación ALAP para el mismo GFD que la figura 1.4a. Estas planificaciones suelen utilizarse como base para generar otras nuevas, en general mejores en cuanto a la minimización del paralelismo.

Los dos objetivos de la planificación (la minimización del número de pasos de control y del paralelismo) son en muchos casos contrapuestos. Esto es debido a que, para reducir el paralelismo, puede ser necesario incrementar el número de pasos de control o viceversa. Sin embargo esto no es siempre así. Por ejemplo, en la figura 1.4 puede verse que la planificación a) sitúa en el mismo paso de control la realización de dos sumas, lo que obligaría a emplear dos sumadores diferentes, además de un restador y un multiplicador, o bien un sumador/restador, un multiplicador y un sumador. La planificación b) plantea un problema similar. En cambio, la c) permite emplear únicamente un sumador y un restador, además del multiplicador. En todos los casos, el número de pasos de control es el mínimo posible.

Figura 1.4. Tres planificaciones de un mismo GFD

Por lo tanto, en muchos casos, el planificador logra disminuir el paralelismo sin incrementar el número de pasos de control. La planificación óptima dependerá siempre de las restricciones impuestas por el usuario y de los objetivos principales que debe conseguir (de tiempo y área), y como hemos visto antes, de la biblioteca de módulos y de las características particulares del diseño.

La planificación de las operaciones en pasos de control es un tema bastante tratado ya por todos los sistemas de SAN, [PaKn87], [Paul88], [SSHF89], [WePa91], y por eso no profundizaremos más en ella.

# 1.2.3. Asignación del Hardware

En esta etapa se decide qué módulos hardware concretos van a realizar cada una de las operaciones del GFD proporcionado por el planificador, dónde se van a almacenar los resultados y qué tipo de interconexiones van a utilizarse para transmitir los datos. Las UFs

pueden escogerse entre las disponibles en una biblioteca, o bien generarlas automáticamente. Los elementos de almacenamiento serán registros y/o memorias. Las interconexiones entre unidades operacionales y unidades de almacenamiento pueden ser buses y/o multiplexores. El resultado es un conjunto de módulos e interconexiones que constituyen la **ruta de datos** del circuito. El objetivo principal de la asignación de hardware es conseguir un circuito con una ruta de datos que tenga un área final mínima.

Para un GFD planificado, se define un espacio de diseño de asignación (EDA) como aquel que contiene todos los posibles diseños que pueden implementar el comportamiento deseado, bajo una serie de restricciones de tiempo (el tiempo de ciclo y el número de etapas). Este EDA puede reducirse bajo ciertas restricciones, a un espacio de diseño de asignación útil.

El algoritmo de asignación debe recorrer este EDA útil, con el fin de encontrar una solución que minimice cierta función de coste. Esta función debe garantizar que los diseños que la minimicen sean aquellos que tienen un área menor. Por lo tanto, debe ser una estimación del área del diseño

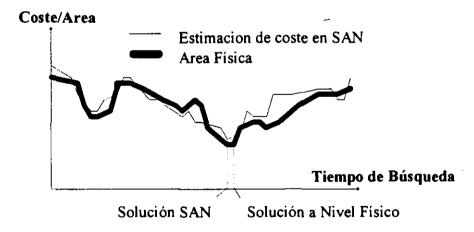

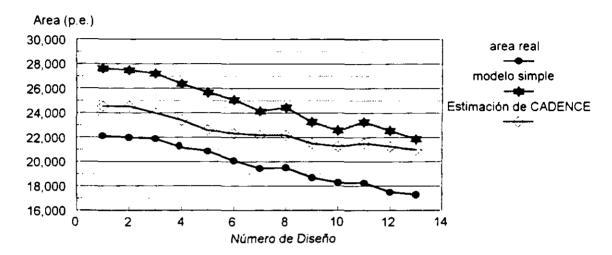

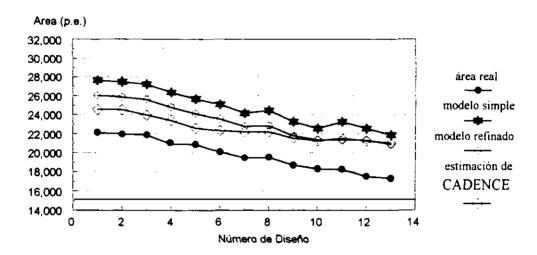

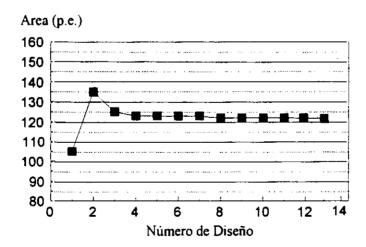

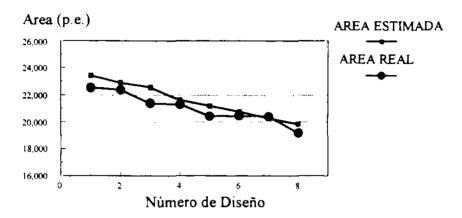

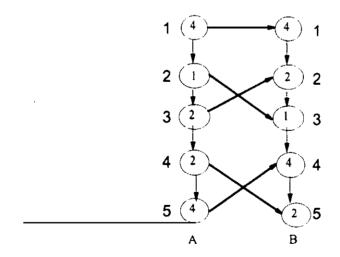

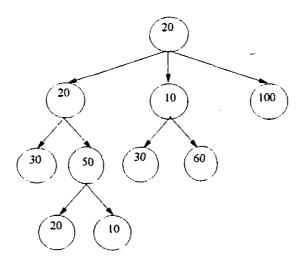

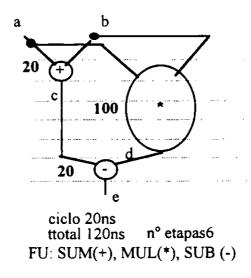

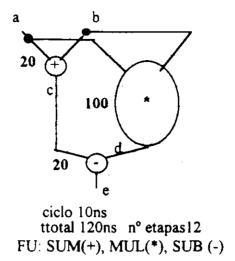

Figura 1.5 Area Física/Coste en SAN

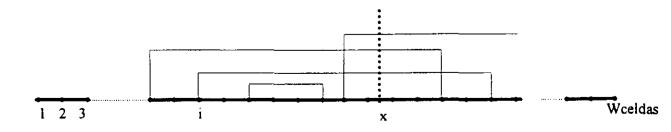

En la figura 1.5 se muestra una representación de un proceso de exploración de un asignador de hardware genérico. En el eje de abcisas se han colocado los distintos diseños en el orden en el cual se encuentran (eje de tiempos), y en el eje de ordenadas el valor dado por la función de

coste. En la misma gráfica se ha incluído el área real, dada por una herramienta CAD, de los mismos diseños.

En una situación óptima, ambas funciones deberían ser iguales, o lo más parecidas posibles, de forma que la estimación del coste de cada diseño coincida con el área real del diseño. Es lo que se denomina una estimación precisa. Sin embargo, en la mayoría de los casos, es suficiente que ambas funciones tengan una forma similar. Así, un diseño con un valor mínimo de la función coste, tendrá también un área real mínima, y el mejor diseño obtenido por el algoritmo de asignación, será el diseño con área real mínima. En este caso diremos que la estimación es fiel.

Por lo tanto, durante un proceso de SAN se necesitan estimaciones fieles, que aseguren que el diseño seleccionado es el diseño con un área real mínima, y lo suficientemente precisas para conseguir diseños que estén dentro de unas especificaciones dadas por el usuario.

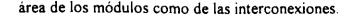

En la figura 1.6 vamos a comparar los resultados que se obtienen utilizando distintas funciones de coste. En la figura 1.6a se ha representado un proceso de obtención de sucesivos diseños (cada uno mejor que el anterior), mediante la exploración del EDA con nuestra herramienta de SAN, FIDIAS, para el ejemplo del filtro elíptico de 5º Orden [HLSB91]. Los algoritmos actuales de FIDIAS, con las estimaciones realizadas en este trabajo de investigación, utilizan una función de coste que contabiliza el área UFs, registros multiplexores e interconexiones. Por eso la gráfica 1.6a coincide con la del área real de los CIs.

En las otras tres gráficas se presentan los resultados generados por otras funciones de coste, que no tienen en cuenta todos los elementos del circuito. En la gráfica 1.6b se representan los costes de los distintos diseños si no se tiene en cuenta el área de las interconexiones. En la gráfica 1.6c sólo se considera el área de UFs y registros, y en la 1.6d sólo la de UFs.

Se puede observar que las gráficas tienen formas muy diferentes. Podemos deducir que la única función de coste fiel, que garantiza la obtención del diseño óptimo, es la que se muestra en la gráfica a, que tiene en cuenta todas las características fisicas del diseño, e incluye tanto el

Figura 1.6 Resultados obtenidos por cuatro funciones de coste distintas

El resto de las funciones no sólo no son lo suficientemente precisas, sino que no permiten distinguir cuál es el diseño óptimo. Por ejemplo, si se usa la función de coste c o la d, la herramienta de SAN consideraría que uno de los diseños óptimos es el 1, cuando su área real es mayor que la del resto de los diseños explorados. De hecho, estas dos funciones dan por mejores precisamente los diseños que tienen mayor área, y por tanto son realmente peores. Por tanto, cualquier función de coste que se utilice en un asignador de hardware debe realizar una estimación global del área del circuito, donde se incluya el área de los módulos y de las interconexiones, y se tenga en cuenta la tecnología utilizada.

Sin embargo, en muchos sistemas de SAN, la asignación no se realiza de forma global. Como

ya se dijo anteriormente, dentro de la asignación de hardware se pueden encontrar dos subtareas: la preasignación de hardware y la asignación de instancias. En cada una de estas fases la información que se dispone del diseño es diferente, y por tanto la función de coste varía. Vamos a ver cuáles son las funciones de estas subtareas y cómo y dónde se necesitan hacer estimaciones.

#### 1.2.3.1. Preasignación de Hardware

La subtarea de preasignación de hardware en algunos sistemas es previa a la planificación temporal y en otros sistemas se realiza conjuntamente con la asignación de hardware. Su función es determinar el número de registros y UFs de cada tipo que se van a utilizar para implementar el circuito. Sólo se decide el número y tipo de los módulos, no las operaciones del GFD que van a ejecutar cada uno de ellos en particular.

En muchos sistemas de SAN, el objetivo de esta tarea es la obtención de curvas árearendimiento [JaPP87], [KuPa90a], [KuRa93], es decir, para cada una de las preasignaciones posibles estimar el área y el retardo del circuito final. De entre todas las posibles soluciones obtenidas, se elige aquella que cumple las restricciones y objetivos impuestas por el usuario (o la mejor de todas, en caso de que haya varias).

Para estimar el rendimiento de un circuito puede tenerse en cuenta el número de pasos de control y el tiempo de ciclo, datos conocidos para una determinada planificación. La estimación del área del circuito puede obtenerse calculando el área mínima de UFs y registros, también para una determinada planificación. Sin embargo, vimos en el apartado anterior que, para obtener soluciones fiables con las tecnologías actuales, es necesario tener en cuenta el área de las interconexiones y multiplexores, así como la tecnología en particular que se va a utilizar. La poca información que se dispone sobre el circuito en este momento dificulta mucho su estimación.

## 1.2.3.2. Asignación de instancias

Esta tarea tiene como función la asignación de variables a registros concretos y la asignación de operadores a UFs concretas. Dependiendo de cómo se realice la asignación, el número de buses, multiplexores e interconexiones punto a punto varía. Como ya se ha mencionado anteriormente, el área de interconexionado es un factor que influye notablemente en los resultados finales

Esta subtarea puede partir de unas restricciones sobre el número de módulos de cada tipo disponibles, si se ha realizado una preasignación de hardware, o bien recibir una restricción en cuanto al máximo coste del diseño permitido. En cualquiera de los dos casos debe tratar de minimizar el coste total del diseño, que como ya hemos visto es una estimación del área fisica de éste

El tipo de las estimaciones que se realizan durante la asignación de hardware varía dependiendo del tipo de algoritmo utilizado, como veremos a continuación. Existen tres tipos de algoritmos fundamentales:

- Constructivos: van asignando el hardware tratando de minimizar el coste final, y la solución que se obtiene es la mejor alcanzable por dicho algoritmo.

- Iterativos: a partir de una solución inicial se van generando nuevas soluciones realizando transformaciones que suponen una mejora de la anterior.

- Iterativo-constructivos: son una mezcla de los dos tipos anteriores. Crean una solución inicial por un método constructivo y van produciendo mejoras sobre ella.

Todos estos algoritmos tienen como finalidad minimizar el área total del CI. La mayoría de los sistemas SAN minimizan el hardware tratando de reutilizar al máximo los registros y las UFs de la ruta de datos. Pero esto no es suficiente. Por ejemplo, la reutilización de una UF lleva consigo la creación de un multiplexor a su entrada (o de un multiplexor con más entradas si ya existía uno), y una o más interconexiones. Las áreas de los módulos y de las interconexiones

dependen de la tecnología que se esté utilizando, de la colocación de los módulos en el circuito final, y de cómo se realice el interconexionado de éstos (tanto de las interconexiones internas de los módulos como de las externas). Por tanto depende de las características fisicas del CI y de las herramientas de diseño, y es necesario estimarlas.

Para cada uno de estos tipos de algoritmos de asignación de hardware las necesidades y condiciones de las estimaciones de área son diferentes.

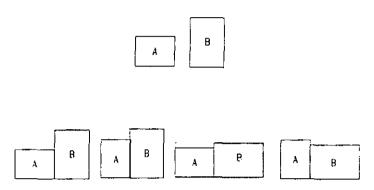

## Algoritmos de tipo constructivo

Durante la asignación de hardware a cada uno de los nodos del GFD es necesario poder decidir entre varias opciones cuál conducirá a la obtención de área mínima. Por ejemplo, es necesario decidir entre reutilizar un determinado módulo o generar uno nuevo, teniendo en cuenta el consiguiente área de multiplexores e interconexiones para cada una de las posibles opciones. Si tenemos una UF cuya salida necesita ser almacenada y existe un registro disponible, es necesario elegir entre reutilizar el registro, al que será necesario añadir un multiplexor y una interconexión entre el multiplexor y el registro, o bien crear un nuevo registro. En ambos casos es necesario estimar el incremento en área que supondrá la creación de una interconexión, y de los módulos que se tengan que añadir, si bien todavía no se conoce el número total de módulos e interconexiones de la ruta de datos del diseño final. Esta estimación de área debe ser muy rápida, ya que se necesita realizar muchas veces durante la generación de un diseño, y debe ser lo suficiente fiel para permitir distinguir entre dos posibles decisiones cuál conducirá al mejor diseño final.

#### Algoritmos de tipo iterativo

Para los algoritmos de tipo iterativo se necesita poder distinguir entre dos o más diseños cuál es el que tiene el área mínima, y también escoger sólo aquellos

diseños que estén dentro de las especificaciones iniciales del sistema. Por lo tanto es necesario estimar el área total de la ruta de datos para cada uno de estos diseños, una vez que ya se conoce el número y tipo de módulos que lo van a formar y sus interconexiones. Esta estimación debe hacerse cada vez que se genere un nuevo diseño, y por lo tanto debe realizarse de forma rápida para que no incremente significativamente la complejidad del algoritmo.

## Algoritmos iterativo-constructivo

Debido a que son un tipo mixto de los dos tipos anteriores, para este tipo de algoritmos es necesario realizar tanto la estimación del área final del circuito como del incremento en área que supone tomar una decisión durante el proceso de diseño.

Por lo tanto, sea cual sea el algoritmo de asignación de hardware utilizado, se deben realizar estimaciones de área rápidas, precisas y sobre todo fiables, que tengan en cuenta las influencias de las características fisicas del circuito. Estas estimaciones unas veces se realizan sobre el diseño global y otras sobre partes del diseño. A lo largo de este trabajo de investigación veremos cómo realizar estas estimaciones de área en cualquiera de los casos anteriores.

#### 1.2.4. Diseño de la Unidad de Control

La siguiente fase de un proceso de SAN es el diseño del controlador. Su función es generar la secuencia de control o microprograma (en el caso de control microprogramado) definitivos empleando la planificación y asignación realizadas anteriormente. Para ello es necesario seleccionar un modelo de Unidad de Control (UC) determinado, ya sea una máquina de estados finitos o algún modelo de unidad de control microprogramada. El área y retardo de la UC depende por una parte del diseño en particular (del número de etapas de control, el tiempo de ciclo y el número de módulos hardware utilizados por el asignador) y por otra de la

tecnología y tipo de UC que se utilice. Por lo tanto en esta fase también es necesario realizar estimaciones de área y retardo.

#### 1.2.5. Control del Proceso de Diseño

Cada una de las subtareas anteriormente explicadas suele realizarse por medio de un módulo software independiente. Sin embargo, estas tareas son interdependientes y las decisiones que se toman en cada una de ellas afectan a los resultados obtenidos por las otras. Por eso, en algunos sistemas de SAN, se plantea la necesidad de un módulo adicional que controle el funcionamiento de todos los otros módulos y permita la interacción entre ellos. Esto posibilitará que todas las herramientas que participan en el diseño se orienten hacia la obtención de los objetivos dados por el usuario.

Este módulo debe decidir en qué momento se ejecuta cada una de las subtareas del proceso de síntesis, qué parámetros de funcionamiento interno utilizan, y cuáles son los parámetros globales del diseño.

También es el encargado de analizar cada uno de los diseños obtenidos, comparar los resultados con los objetivos deseados, y, en caso necesario, volver a diseñar con otros parámetros. De esta forma se consigue un sistema en lazo cerrado que permite la realimentación entre los distintos módulos operativos.

Este tipo de controlador necesita analizar los diseños obtenidos para ver si se cumplen los objetivos especificados, es decir, el coste en área y el rendimiento. También necesita realizar medidas sobre el retardo y área de los módulos hardware que deben ser tenidas en cuenta durante la planificación y la asignación de hardware a la hora de tomar decisiones.

#### 1.3. Conexión con herramientas de Diseño

Todos las ventajas anteriormente descritas de una herramienta SAN se verían muy disminuidas

si no fuera posible generar automáticamente el layout del diseño a partir de la descripción estructural generada, ya que la interacción manual durante este último proceso incrementaría excesivamente el tiempo total de diseño. El módulo encargado de la asignación de hardware produce como salida la estructura definitiva del circuito digital, en forma de lista de componentes e interconexiones, o bien en forma gráfica. Por su parte, la salida del módulo encargado de la generación del controlador es la secuencia de estados o microprograma que, junto con el modelo de UC elegido, constituirá el hardware de control del sistema digital diseñado.

Si nos fijamos de nuevo en la figura 1.1, se puede observar que para obtener el layout final del circuito queda realizar la generación de módulos que lo componen y la colocación e interconexionado de estos, siempre cumpliendo unas reglas impuestas por la tecnología de fabricación. Aunque existen un conjunto amplio de estilos de diseño, que se presentan en el Apéndice A, esta última fase sólo tiene sentido realizarla en un estilo que tenga los mismos objetivos que la SAN. No tendría sentido automatizar el proceso de SAN para realizar luego el diseño con un estilo full-custom, que requiere una gran cantidad de tiempo, y además no es válido para diseños muy complejos. Tampoco sería lógico utilizar una tecnología basada en PLAs y ROM, donde se desaprovecha una gran cantidad de área, con lo cual todo el ahorro realizado por la herramienta de SAN se vería contrarrestado.

Por eso, los circuitos implementados con una herramienta de SAN debe fabricarse en un estilo de diseño basado en celdas estándar, macroceldas o arrays de puertas. Para estos estilos, las tareas de generación de módulos, colocación e interconexionado pueden realizarse por herramientas CAD de las que hemos hablado anteriormente, y que a partir de ahora también llamaremos herramientas de Sintesis de Bajo Nivel (SBN) o herramientas de diseño. Estas herramientas suelen ser específicas para cada uno de los estilos de diseño.

Por tanto, la generación del circuito final partiendo de la descripción de su comportamiento puede realizarse en dos fases:

La primera utiliza una herramienta de SAN y obtiene como salida diseños a nivel

RTL.

La segunda utiliza una herramienta CAD que, partiendo del nivel RTL generado por la herramienta de SAN, realiza la generación de módulos y su colocación e interconexionado final.

La conexión entre ambas herramientas puede hacerse automáticamente, con lo cual el proceso de diseño estaría totalmente automatizado.

La fase de generación de módulos puede ser independiente y previa a la Síntesis de Alto Nivel, formando una biblioteca de módulos, que estaría disponible para cualquier diseño, desde las primeras fases de la síntesis. Además, esto facilita la utilización de bibliotecas diferentes según la tecnología de fabricación, lo cual permite que el rápido avance de la tecnología no sea un factor crítico en la validez de la herramienta SAN.

Por otra parte, sabemos que el planificador y el asignador de hardware reciben como entrada una biblioteca de módulos (figura 1.2). Es posible almacenar datos en ella sobre cada uno de los distintos elementos hardware que la componen, que faciliten la estimación de su área y retardo. En [JRDK94] se demuestra experimentalmente la influencia de las variaciones del área y retardo de los módulos de la biblioteca en el layout final, y la imposibilidad de tratar los módulos como componentes con un tamaño y retardo constante. Como la colocación e interconexionado de módulos se realiza de forma global para todo el diseño RTL, la forma y tamaño de las componentes varía de unos diseños a otros. Por lo tanto, la biblioteca debe almacenar información física para una tecnología particular que permita estimar los valores de área y retardo de los módulos en el diseño final.

Por otra parte, se ha visto anteriormente que, debido a las influencias del nivel físico sobre el diseño, y para respetar las restricciones impuestas por el usuario en la SAN, así como para medir la calidad de los diseños obtenidos durante el proceso de síntesis, es necesario realizar una serie de estimaciones tanto del área de los módulos e interconexiones (coste) como sobre el retardo de estos, que nos dará una idea de la velocidad del diseño. De aquí surge la

necesidad de realizar la conexión de nuestra herramienta SAN con una herramienta de SBN, con la cual poder estudiar cómo trabajan las herramientas de diseño y poder evaluar nuestras predicciones.

El diseño físico previo a la SAN de cada uno de los módulos de la biblioteca permite almacenar en ésta información física sobre aquellos, como puede ser el área de sus celdas estándar (o macroceldas), el retardo, el consumo, las interconexiones internas, etc. Toda esta información la pueden utilizar los módulos de planificación, asignación de hardware, etc. para tomar sus decisiones. De esta forma tanto las medidas parciales como las finales sobre los diseños serán mucho más realistas.

La conexión entre una herramienta de SAN y otra de SBN se puede realizar traduciendo el camino de datos y la Unidad de Control que proporciona la herramienta SAN, a un lenguaje estándar como EDIF (Electrical Design Interchange Format) o VHDL, que son aceptados como entrada por la mayoría de las herramientas de SBN.

En definitiva, podemos concluir que el uso conjunto de herramientas automáticas de síntesis complementarias (herramientas de síntesis de alto nivel, por un lado, y de bajo nivel por otro) puede permitir automatizar el proceso de diseño prácticamente en su totalidad, y acceder a todas las ventajas que esta automatización conlleva. La automatización total debe estar controlada por el módulo controlador de diseño, que decidirá qué diseño es el que se va a sintetizar y una vez obtenido el layout comprobará que se cumplen las restricciones impuestas por el usuario

## 1.4. Conclusiones

A lo largo de este capítulo se ha justificado la necesidad de realizar estimaciones de área y retardo durante la SAN, teniendo en cuenta las influencias de las características físicas del circuito integrado.

En primer lugar hemos visto que para realizar la selección del tiempo de ciclo, se deben tener en cuenta la biblioteca de módulos disponible, los retardos del interconexionado, y las restricciones del usuario en cuanto al área y tiempo de ejecución del circuito, así como realizar un estudio global del GFD. El retardo del interconexionado es un dato que no se conoce hasta que no se ha generado el layout, y por tanto es necesario estimarlo.

En segundo lugar hemos demostrado como cualquier función de coste que se utilice en un asignador de hardware debe ser una aproximación al área real del circuito. Este área es la suma del área de los módulos y de las interconexiones, que a su vez dependen de la tecnología que se esté utilizando, de la colocación de los módulos en el circuito final, y de cómo se realice el interconexionado de éstos (tanto de las interconexiones internas de los módulos como de las externas). Por tanto depende de las características fisicas del CI y de las herramientas y tecnologías de diseño, y es necesario estimarlas.

También se observó que durante la asignación de hardware se necesitan realizar diversos tipos de estimaciones, dependiendo del tipo de algoritmo utilizado:

- Para los algoritmos de tipo constructivo era necesario estimar qué decisión entre todas las posibles conduciría a un diseño con un área mínima. Estas estimaciones se realizan cuando todavía no se conocen todos los elementos que integran el circuito.

- Para los algoritmos iterativos era necesario estimar si un diseño es mejor o peor que otro. Estas estimaciones se realizan cuando se conocen todos los elementos que integran ambos diseños.

En todos los casos las estimaciones se necesitan realizar muchas veces durante un proceso de síntesis, y por tanto deben ser muy rápidas.

Por lo tanto, en SAN se necesita un método de estimación del área muy **rápido** (tanto del área de los módulos como de las interconexiones), que más que permitirnos obtener un valor exacto de área final del diseño, tenga suficiente **fidelidad** para:

- Permitir tomar decisiones sobre si un diseño es mejor que otro.

- Decidir si un diseño está dentro de unas especificaciones dadas por el usuario

- Permitir seleccionar entre dos posibles decisiones la que conduce a un área mínima

También se planteó la necesidad de realizar la conexión de la herramienta de SAN con una herramienta de diseño con dos objetivos fundamentales:

- Realizar una automatización total del proceso de diseño.

- Estudiar las influencias del nivel físico en las decisiones que se toman durante la SAN, y recopilar la información necesaria para poderlas tener en cuenta durante todas las fases de la síntesis.

Sin embargo, la mayoría de los sistemas de SAN no realizan todas las estimaciones anteriormente presentadas. No tenemos información sobre ningún sistema que realice estimaciones del retardo de las interconexiones para obtener el tiempo de ciclo y asegurar el correcto funcionamiento del circuito. Existen algunos sistemas que tienen en cuenta de alguna forma el área de las interconexiones, y otros que estiman el área de los módulos en el diseño final, pero en ningún caso estas estimaciones cumplen todos los requisitos anteriores.

El objetivo principal de este trabajo de investigación es estudiar las influencias de las características fisicas del CI sobre el área y retardo del los diseños, y diseñar técnicas de estimación rápidas, precisas y fieles para todas las fases de la SAN. Se presentará un método de estimación de área durante la asignación de hardware válido para todos y cada uno de los tipos de algoritmos presentados. Como estas influencias dependen de la tecnología de diseño utilizada, y el estudio para todas ellas es un trabajo de una extensión excesiva, se particulizará el estudio para celdas estándar. Sin embargo, muchas de las ideas propuestas pueden utilizarse para macroceldas y arrays de puertas.

Estas estimaciones pueden utilizarse también durante la preasignación de hardware y la generación del control. También se verá cómo es posible estimar el retardo de las interconexiones. Además, se realizará la conexión de una herramienta de SAN con una

herramienta CAD, así como la automatización del proceso de diseño completo.

Pero antes de presentar estos métodos de estimación, en el capítulo 2 se realiza un repaso de los principales sistemas de que elaboran algún tipo de estimación del área de interconexionado. Veremos sus ventajas y sus inconvenientes, y la necesidad de realizar nuevas estimaciones más precisas y rápidas.

En el capítulo 3 se estudiará el sistema FIDIAS, que es un sistema de SAN dentro del cual se integra este trabajo de investigación. Se verá que en este sistema, como en todos, también es necesario realizar estimaciones, y cómo y dónde se deben integrar éstas.

En el capítulo 4 se realizará un estudio de la metodología de trabajo de las herramientas de CAD, y de las características físicas de los CIs. A partir de este estudio, se realizarán estimaciones del área de las interconexiones y de los módulos del CI, y se integrarán dentro del sistema FIDIAS. Veremos también que estas estimaciones se pueden integrar en cualquiera de los tipos de algoritmos de asignación vistos anteriormente.

En los capítulos 5 y 6, y a partir de las estimaciones del área de las interconexiones del capítulo 4, veremos la forma de calcular el retardo de éstas. Se realizará un estudio completo sobre el retardo del interconexionado, y sobre cómo se puede incluir éste en el cálculo del tiempo de ciclo. También veremos un algoritmo de estimación del tiempo de ciclo que tiene en cuenta la biblioteca de módulos, las restricciones del usuario y que estudia de forma global el GFD.

| • |   |   |  |

|---|---|---|--|

|   |   |   |  |

|   |   |   |  |

|   |   |   |  |

|   |   |   |  |

|   |   |   |  |

|   |   |   |  |

|   |   |   |  |

|   |   |   |  |

|   |   |   |  |

|   |   | • |  |

|   |   |   |  |

|   |   |   |  |

|   |   |   |  |

|   |   |   |  |

|   |   |   |  |

|   |   |   |  |

|   |   |   |  |

|   |   |   |  |

|   |   |   |  |

|   | - |   |  |

|   |   |   |  |

|   |   |   |  |

|   |   |   |  |

|   |   |   |  |

|   |   |   |  |

|   |   |   |  |

|   |   |   |  |

|   |   |   |  |

|   |   |   |  |

|   |   |   |  |

|   |   |   |  |

|   |   |   |  |

|   |   |   |  |

|   |   |   |  |

|   |   |   |  |

|   |   |   |  |

|   |   |   |  |

|   |   |   |  |

|   |   |   |  |

|   |   |   |  |

|   |   |   |  |

|   |   |   |  |

|   |   |   |  |

## Capítulo 2

# Técnicas de Estimación de las Características Físicas

### 2.1. Introducción

Muy pocos sistemas de SAN tienen en cuenta las características del nivel físico. Sin embargo, con la tecnología VLSI, una gran parte del área del CI se consume en cableado y el retardo de las interconexiones es muy significativo. Ya McFarland [McFa87] apuntó la gran importancia de tener en cuenta las características físicas del diseño en SAN. Posteriormente Parker y colaboradores [PaGH91] pusieron de manifiesto las variaciones que dichas características producen en las curvas área-rendimiento de los diseños producidos.

Por otra parte, en el capítulo anterior vimos la necesidad de realizar estimaciones del área de los módulos y de las interconexiones en varias de las distintas fases de la SAN. También se planteó la importancia de considerar el retardo de las interconexiones durante la planificación de operaciones, a pesar de lo cual la mayoría de los sistemas sólo tienen en cuenta el de los módulos. La estimación de los retardos de las interconexiones sólo puede realizarse a partir de las longitudes de éstas, por lo cual sólo los sistemas que estiman la longitud de las interconexiones pueden calcular su retardo.

A lo largo de este capítulo vamos a revisar los sistemas que de alguna forman tienen en cuenta la influencia de las características físicas en el área de las distintas partes que integran el circuito. Entre todos estos sistemas, señalaremos los que estiman el retardo de las interconexiones.

Algunos de los sistemas de SAN sólo pueden generar las estimaciones de área a nivel RTL, cuando ya se conocen el número de módulos y de interconexiones. Otros permiten realizar algunas estimaciones durante la generación de un diseño, cuando la información sobre éste aún no es completa. Pero ninguna de estas estimaciones sobre área cumple los requisitos que vimos en el capítulo anterior: baja complejidad, fidelidad y precisión.

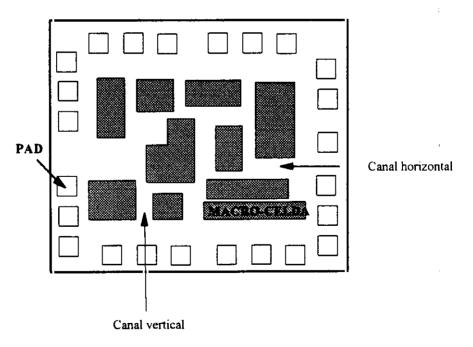

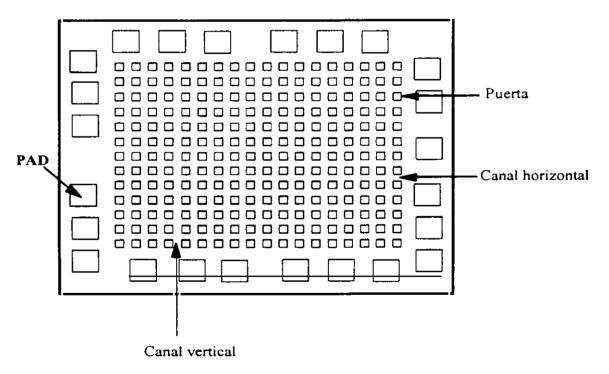

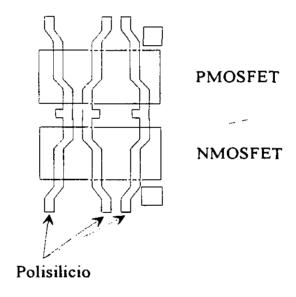

La mayoría de los métodos capaces de predecir el área de un diseño con suficiente exactitud, teniendo en cuenta el área de interconexionado, necesitan la información completa sobre el diseño y generan la estimación para un tipo de tecnología determinada. Estos métodos suelen estar integrados en las herramientas de SBN, y predicen el área de un circuito dada su descripción como un conjunto de celdas estándar (algunos permiten incluir macroceldas) o arrays de puertas y sus interconexiones, con el fin de disminuir el número de iteraciones necesarias para realizar un *floorplanning* (ver Apéndice B) correcto. Estas estimaciones suelen ser bastante precisas, con un error inferior al 10%, y la herramienta de SBN sólo necesita elaborarlas una vez. Pero como la información que necesitan manejar estos algoritmos de estimación es muy grande, la complejidad suele ser muy elevada, y no es conveniente integrarlos dentro de una herramienta de SAN, donde es necesario generar las estimaciones un gran número de veces. Sin embargo, es interesante repasar algunos de estos métodos para ver qué posibilidades presentan.

A lo largo de este capítulo vamos a exponer las principales técnicas de estimación de área clasificándolas en dos grupos fundamentales: las que se elaboran durante el proceso de SAN y las que se realizan a nivel de celdas estándar y arrays de puertas. Las primeras las denominaremos "Técnicas de Estimación durante la SAN" y las segundas "Técnicas de Estimación de Bajo Nivel". En el primer grupo presentaremos también los principales sistemas de SAN que, de alguna forma, tienen en cuenta las interconexiones en la optimización del diseño.

Como veremos, en general, las técnicas pertenecientes al primer grupo no son lo suficientemente fieles, mientras que las del segundo grupo son muy precisas, pero tienen una

complejidad demasiado elevada para ser utilizadas dentro de un proceso de SAN. Por eso surge la necesidad de obtener nuevas técnicas de estimación de área que reúnan las propiedades de ambos tipos: la precisión de las segundas y la baja complejidad de las primeras.

Nota. A lo largo de este capítulo utilizaremos las palabras conexión e interconexión como sinónimos. Una red se refiere a una conexión que una más de dos elementos. También serán sinonimos área de interconexionado y área de cableado.

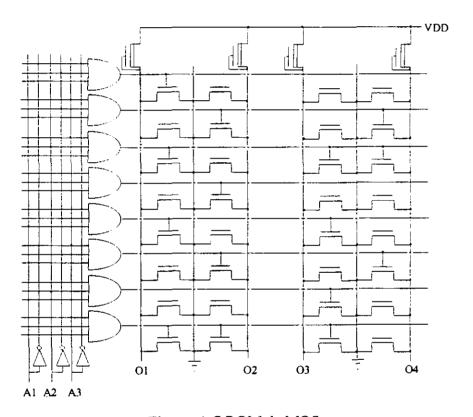

## 2.2. Estimaciones de área durante un proceso de SAN