# UNIVERSIDAD COMPLUTENSE DE MADRID

# FACULTAD DE CIENCIAS FÍSICAS

# OPTIMIZACIÓN DEL DISEÑO FÍSICO DE CIRCUITOS DIGITALES ORIENTADO A DISPOSITIVOS RECONFIGURABLES

# MEMORIA PARA OPTAR AL GRADO DE DOCTOR PRESENTADA POR

Juan de Vicente Albendea

Bajo la dirección del doctor Juan Lanchares

Madrid, 2001

ISBN: 84-669-1771-3

# OPTIMIZACIÓN DEL DISEÑO FÍSICO DE CIRCUITOS DIGITALES ORIENTADO A DISPOSITIVOS RECONFIGURABLES

# JUAN DE VICENTE ALBENDEA

Universidad Complutense de Madrid Facultad de Ciencias Físicas Tesis Doctoral

Madrid, 2001

#### Resumen

Los dispositivos reconfigurables están revolucionando los procesos de desarrollo y producción de sistemas digitales. Debido a la complejidad creciente de los sistemas, y para sacar el máximo partido a los recursos que ofrecen los dispositivos reconfigurables, es imprescindible la automatización de los procesos implicados en el desarrollo de circuitos orientado a estos dispositivos. En esta tesis se señalan algunos puntos débiles de las herramientas de ubicación y cableado actuales, y se desarrollan métodos y estrategias flexibles con el objetivo de hacer frente a las exigencias actuales y futuras en el diseño sobre sistemas reconfigurables. Entre los principales resultados prácticos de la tesis podemos destacar: un método nuevo de Optimización Combinatoria adaptativo basado en principios termodinámicos, una nueva aproximación polinómica al Árbol de Steiner Mínimo Rectilíneo, un método de ubicación y rutado simultáneos sobre FPGAs, y un método de partición sobre mallas de FPGAs basado en ubicación y rutado.

A mis padres, a Nuria y a Pablo

## **Agradecimientos**

En primer lugar quiero agradecer a Juan Lanchares por el magnífico trabajo desarrollado en la dirección de esta tesis. Su confianza, esfuerzo y apoyo me han permitido ir cubriendo distintos objetivos necesarios para la realización de esta investigación.

También quiero dar las gracias a Juan Manuel Sánchez por su dirección durante los dos primeros años del doctorado. Agradecer asimismo a Román Hermida por el interés mostrado en la investigación, y por el acertado trabajo realizado en la corrección tanto de la tesis como de los distintos artículos sobre los que se asienta.

Me gustaría dar las gracias a todos mis compañeros de la ETSIAN. Especialmente a Miguel Ángel Alvaro por su valiosa discusión técnica sobre distintas cuestiones suscitadas a lo largo de este trabajo, a Manuel Laguna, Javier Lozano, Vicente Gallego, Mauricio Bados y Alfredo Vizcaya por su generosa ayuda a lo largo de estos años, y a los sucesivos directores de la escuela por el apoyo recibido.

Agradecer a Francisco Tirado por la confianza mostrada al incluirme en el proyecto de investigación CICYT TIC 99-0474 del cual es investigador principal. A José Ignacio Hidalgo y Oscar Garnica por su ayuda en distintos aspectos de la investigación. A Manuel Ortega, Antonio Vaquero y Milagros Fernández por su orientación inicial, y en general a todos los miembros del Departamento de Arquitectura de Computadores y Automática de los cuales he recibido un gran apoyo. Quiero también dar las gracias a Vaughn Betz y Jonathan Rose de la Universidad de Toronto por facilitarme el conjunto de benchmarks utilizados en esta tesis.

Gracias a mis padres, hermanos y familia política por su cariño y ayuda, los cuales han facilitado enormemente este trabajo. Agradecer a mis amigos por el apoyo recibido, y dedicar un recuerdo especial a Gerardo, que sin duda se habría alegrado en este momento.

Finalmente, quiero agradecer a mi mujer Nuria y a mi hijo Pablo por su amor, paciencia y comprensión, los cuales han sido mi mayor soporte.

# Tabla de contenidos

| Resun | nen                                                         | ii |

|-------|-------------------------------------------------------------|----|

| Agrad | decimientos                                                 | iv |

| Capít | ulo 1                                                       |    |

| Intro | oducción                                                    | 1  |

| Capít | ulo 2                                                       |    |

| Arqu  | nitectura de los sistemas reconfigurables y herramientas de |    |

| diseñ | io automático                                               |    |

| 2.1   | Los sistemas reconfigurables                                | 7  |

| 2.2   | Ciclo de diseño VLSI                                        | 12 |

| 2.3   | Estilos de diseño físico                                    | 14 |

| 2.4   | Familias de FPGAs                                           | 15 |

| 2.5   | Arquitectura de las FPGAs                                   | 17 |

| 2.6   | Diseño físico sobre FPGAs                                   | 19 |

| 2.0   | 6.1 Ubicación sobre FPGAs                                   | 21 |

| 2.0   | 6.2 Cableado sobre FPGAs                                    | 29 |

| 2.7   | Arquitectura de los Sistemas Multi-FPGA                     | 34 |

| 2.8   | Diseño físico sobre Sistemas Multi-FPGA                     | 38 |

| Capít | ulo 3                                                       |    |

| Ubica | ación en FPGAs mediante <i>Optimización Natural</i>         |    |

| 3.1   | Ubicación mediante Enfriamiento Simulado                    | 44 |

| 3.2   | Optimización Natural                                        | 51 |

| 3.3   | Enfriamiento Simulado vs Optimización Natural               | 56 |

| 3.4   | Conclusión                                                  | 61 |

# Capítulo 4

| Ubica  | ación en FPGAs mediante                                                       |

|--------|-------------------------------------------------------------------------------|

| Optin  | nización Combinatoria Termodinámica                                           |

| 4.1.   | Introducción                                                                  |

| 4.2.   | Termodinámica64                                                               |

| 4.3.   | Método de Optimización Combinatoria Termodinámica                             |

| 4.4.   | Resultados experimentales78                                                   |

| 4.5.   | Conclusión81                                                                  |

| Capít  | ulo 5                                                                         |

| Estin  | nación de la congestión en la fase de ubicación:                              |

| Valor  | es Esperados de Ocupación                                                     |

| 5.1    | Introducción                                                                  |

| 5.2    | Congestión85                                                                  |

| 5.2    | 2.1 Congestión media                                                          |

| 5.2    | 2.2 Congestión local                                                          |

| 5.3    | Valores esperados de ocupación (VEO)                                          |

| 5.3    | 3.1 Cálculo de los valores esperados de ocupación                             |

| 5.3    | 3.2 Función de coste basada en los Valores Esperados de Ocupación96           |

| 5.4    | Resultados experimentales                                                     |

| 5.5    | Revisión crítica de la aplicabilidad del modelo y definición de nuevos        |

|        | objetivos98                                                                   |

| Capítı | ulo 6                                                                         |

| Medi   | da de la congestión en la fase de ubicación:                                  |

| Regio  | ones de Steiner Rectilíneas                                                   |

| 6.1    | Introducción                                                                  |

| 6.2    | Regiones de Steiner Rectilíneas                                               |

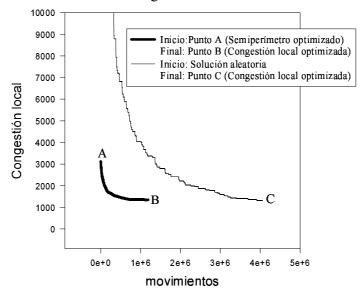

| 6.3    | Optimización de la ubicación en etapas orientada a evitar la congestión local |

|        | (U-RSR)                                                                       |

| 6.4    | Cableado global basado en el algoritmo RSR (CG-RSR)        | 116  |

|--------|------------------------------------------------------------|------|

| 6.5    | Comparación de resultados entre VPR y UCG-RSR              | 119  |

| 6.6    | Conclusiones                                               | 121  |

| Capít  | ulo 7                                                      |      |

| Méto   | do PUR para la partición de circuitos en Sistemas Multi-   | FPGA |

| con to | opología de malla                                          |      |

| 7.1    | Introducción                                               | 122  |

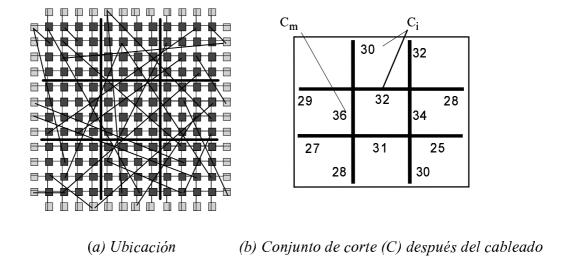

| 7.2    | Modelo para los sistemas MFPGAs y formulación del problema | 125  |

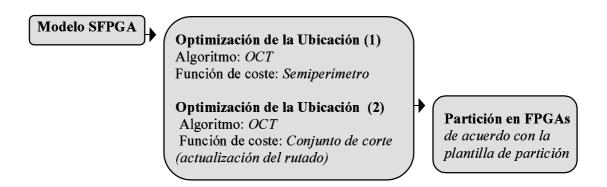

| 7.3    | Optimización del conjunto de corte mediante el método PUR  | 127  |

| 7.4    | Aplicación del método PUR a circuitos concretos            | 131  |

| 7.5    | Conclusión                                                 | 136  |

| Capít  | ulo 8                                                      |      |

| Princ  | cipales aportaciones de la tesis                           |      |

| y futi | uras líneas de investigación                               | 138  |

| Refere | encias                                                     | 143  |

# Capítulo 1

### Introducción

Las FPGAs (Field Programmable GateArrays) [Xil] son dispositivos de lógica programable por el usuario que proporcionan un método rápido y barato para el desarrollo de circuitos. Sus características de flexibilidad y reconfigurabilidad proporcionan interesantes ventajas para el apoyo al diseño y a la producción de sistemas digitales. Las FPGAs fueron introducidas inicialmente, a mediados de los ochenta, como una tecnología de propósito específico. Sin embargo, hoy en día su ámbito de aplicación se extiende a distintas áreas como son la emulación lógica, el prototipado rápido, los sistemas multimodo, las computadoras reconfigurables o problemas concretos de supercomputación.

Para obtener beneficio de las posibilidades que ofrecen los sistemas basados en FPGAs, es necesario disponer de herramientas que automaticen los procesos implicados en el diseño y desarrollo de circuitos orientado a estos dispositivos. Así, se debe facilitar la carga automática de algoritmos sobre las FPGAs, de la misma forma que se cargan programas sobre las computadoras de propósito general. Mientras que la implementación de un algoritmo sobre una computadora de propósito general da como resultado un programa, en el caso de la carga de un algoritmo sobre una FPGA, el resultado es un circuito dedicado. Este circuito dedicado puede satisfacer distintas aspiraciones como son: sustituir el software por hardware para proporcionar mayores prestaciones, emular diseños hardware para depurar prototipos de circuitos integrados, o diseñar sistemas digitales fácilmente actualizables. La carga de un algoritmo sobre una FPGA es un proceso complejo, que normalmente se realiza a través de las distintas etapas correspondientes al diseño de circuitos VLSI (*Very Large Scale Integration*)

Una etapa importante del ciclo de diseño VLSI orientado a FPGAs es el diseño físico. El diseño físico consiste en la transformación de la representación circuital de un

sistema, en una representación geométrica sujeta a las reglas impuestas por la tecnología de fabricación. Las FPGAs son dispositivos formados por un conjunto de elementos lógicos y de interconexión programables. Al ser dispositivos prefabricados, el ciclo diseño físico difiere en algunos aspectos del diseño físico orientado a otras tecnologías. Así, la anchura de los canales de la FPGA, a través de los cuales se realiza el cableado del circuito, constituye una ligadura inflexible que requerirá, en muchas ocasiones, una distribución cuidadosa de las redes que componen el circuito sobre la FPGA. Como las alternativas para realizar esta distribución crecen de forma exponencial con el tamaño del circuito, el ciclo de diseño físico de un sistema basado en FPGAs se convierte en un proceso complejo, incluso para tamaños moderados de circuito. Por este motivo, el diseño físico de un circuito sobre una FPGA normalmente se descompone en diversas etapas como son: la partición, la ubicación y el rutado. La partición divide el circuito lógico en partes, de forma que cada una se pueda implementar mediante la programación de un bloque lógico configurable prefabricado. En la ubicación se realiza la asignación específica de los bloques lógicos a bloques físicos. Y por último, el rutado selecciona los recursos para realizar las conexiones entre los distintos bloques físicos.

En cada una de estas etapas, las herramientas de diseño físico deben ser capaces de administrar correctamente los recursos lógicos y de cableado. Por ejemplo, una correspondencia inadecuada entre bloques lógicos y físicos provoca la congestión de señales, y por lo tanto, el agotamiento de los recursos de cableado. Ello obliga al usuario a recurrir a FPGAs de mayor tamaño y coste, provocando normalmente una infrautilización de los recursos lógicos de los sistemas basados en FPGAs. Por lo tanto, las herramientas de diseño automático se deben encargar de hacer cumplir las restricciones impuestas por los sistemas. Entre estas restricciones destaca, en el caso de las FPGAs, la escasez de líneas de interconexión entre los elementos lógicos que las componen, mientras que en el caso de los sistemas compuestos por varias FPGAs o sistemas Multi-FPGAs, su principal carencia la constituye el reducido número líneas de comunicación disponibles entre FPGAs. En ambos casos, una ubicación descuidada hace imposible el rutado.

Un aspecto importante a considerar en la automatización del diseño físico es la complejidad de tipo NP de los problemas tratados. Como ya comentamos anteriormente, el número de alternativas o configuraciones posibles del circuito, crece de forma exponencial con el tamaño de éste. Ello hace que la búsqueda de las mejores soluciones, o simplemente de soluciones viables, sea computacionalmente cara. El éxito de las herramientas de diseño automático estará determinado fundamentalmente por los algoritmos utilizados para la selección de soluciones, y por los criterios que se establezcan para estimar o evaluar la calidad de éstas.

En cuanto a los algoritmos para la selección de soluciones, la mayoría de las herramientas CAD (Computer Aided Design) abordan estos problemas mediante algoritmos de optimización combinatoria como el Enfriamiento Simulado o los Algoritmos Genéticos. En la actualidad, el Enfriamiento Simulado (ES) es uno de los algoritmos más utilizados, debido a que proporciona buenos resultados en tiempos aceptables. Su ámbito de aplicación se extiende también a multitud de problemas derivados de las ciencias e ingenierías. Así, aparece referenciado en áreas tan dispares como las redes neuronales, las finanzas o el análisis de combate. Sin embargo, el ajuste fino de este algoritmo para los distintos problemas y funciones de coste, requiere costosos estudios experimentales para determinar el valor de los parámetros que lo controlan. Debemos tener en cuenta que la resolución de los problemas descritos anteriormente, exige la exploración de múltiples funciones de coste con el objetivo de determinar la más idónea para cada problema. De forma que la tarea asociada al ajuste de los parámetros para cada una de esas funciones de coste, puede llegar a consumir gran parte de los esfuerzos de la investigación. Por lo tanto, la automatización del ajuste de parámetros del método de optimización combinatoria utilizado podría ser muy beneficiosa para el éxito de la investigación.

Por otra parte, podemos establecer diversos criterios para discriminar la calidad de las soluciones exploradas por las herramientas de diseño físico. Estos criterios pueden ir desde estimaciones poco fiables pero rápidas, a medidas más detalladas y lentas. Como consecuencia, la elección de uno u otro criterio, se debe realizar teniendo en cuenta diversos factores como son: la complejidad de la estimación o medida, el tiempo de

computo de ésta, el tamaño de la instancia del problema y el algoritmo de optimización utilizado, la calidad exigida para la solución, la configuración de partida, etc. En el caso de la ubicación, para discriminar entre soluciones en el proceso de búsqueda, es habitual recurrir a una estimación rápida del cable necesario para rutar el circuito. Estas estimaciones permiten abordar el problema de la ubicación de grandes circuitos, pero a costa de producir ubicaciones subóptimas. Aunque sería deseable la medida directa de la calidad de las ubicaciones basada directamente en el cableado, esta medida es excesivamente costosa en tiempo cuando se recurre a las actuales herramientas de cableado. En cuanto a la partición de circuitos orientada a mallas de FPGAs, muchas de las herramientas desarrolladas hasta la fecha no tienen en cuenta el consumo de recursos debido a la conexión entre FPGAs no adyacentes, y por lo tanto, dan lugar a soluciones poco realistas.

De acuerdo con los problemas expuestos, el objetivo de este trabajo de investigación ha ido dirigido a la obtención de métodos eficaces para el diseño físico de circuitos sobre sistemas basados en FPGAs. Para alcanzar ese objetivo es necesario cubrir diversas etapas, tanto en el diseño físico orientado a FPGAs como a sistemas Multi-FPGAs, que resuelvan los problemas planteados. A continuación se resumen los objetivos comunes y específicos para cada uno de estos sistemas:

- Estudio e investigación de **métodos de optimización combinatoria** que, no sólo generen soluciones de calidad, sino que también proporcionen una mayor flexibilidad para facilitar y mejorar el tratamiento de los problemas considerados. En concreto, reducción del esfuerzo y tiempo invertido en el ajuste de los parámetros de los algoritmos del *Enfriamiento Simulado*, y en la medida de lo posible, automatización de este proceso. La automatización del ajuste de parámetros permitiría concentrar el esfuerzo en la investigación de nuevas funciones de coste que contemplen los problemas específicos tanto en FPGAs como en mallas de FPGAs.

- Estudio de los problemas de congestión producidos en el diseño físico orientado a FPGAs, y desarrollo de métodos que permitan evitarla en las dos etapas más influyentes

del ciclo de diseño físico: fases de ubicación y cableado. En lo que a la fase de ubicación se refiere, estudio de su influencia en la congestión, determinando las virtudes y carencias de las funciones de coste comúnmente utilizadas. Desarrollo de nuevos métodos y funciones de coste que aborden los problemas de congestión. En cuanto a la fase de cableado, estudio de los algoritmos de cableado actuales determinando las causas de su lentitud, y búsqueda de algoritmos de cableado alternativos que sean rápidos y no comprometan la calidad de las soluciones.

• Análisis del problema del diseño físico de circuitos orientado a Sistemas Multi-FPGA con topología de malla. Estudio del consumo de recursos de cableado en la conexión entre FPGAs no adyacentes, y desarrollo de métodos y estrategias dirigidas a mejorar los bajos porcentajes de utilización de la lógica que presentan estos sistemas.

A continuación describimos la estructura de esta tesis que se desarrolla según el siguiente esquema:

En el capítulo 2 se introducen los distintos estilos de diseño de circuitos integrados. Se destacan los sistemas reconfigurables y las diferentes familias de FPGAs. Posteriormente, se realiza una descripción general de los elementos fundamentales que componen tanto las FPGAs como los sistemas Multi-FPGA. Se exponen los problemas derivados del diseño físico sobre FPGAs y sistemas Multi-FPGA, y se analizan las virtudes y defectos de los procedimientos y herramientas desarrollados hasta la fecha.

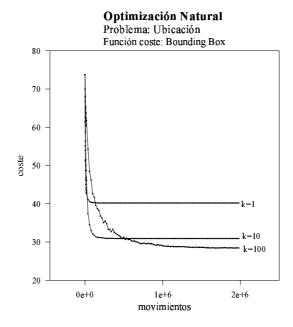

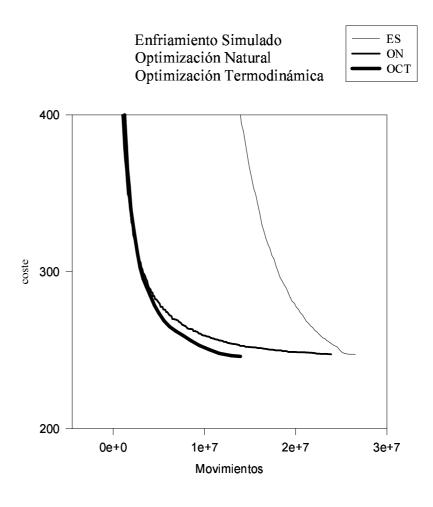

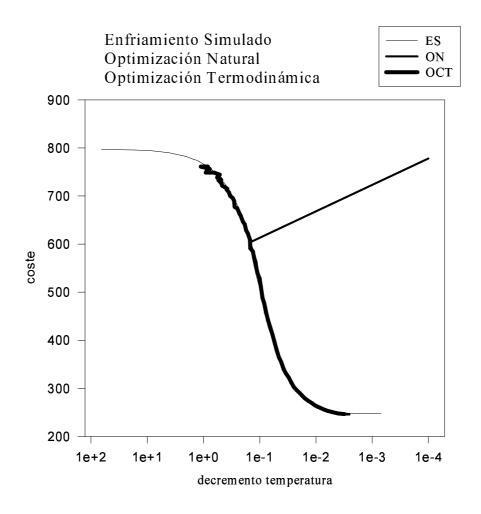

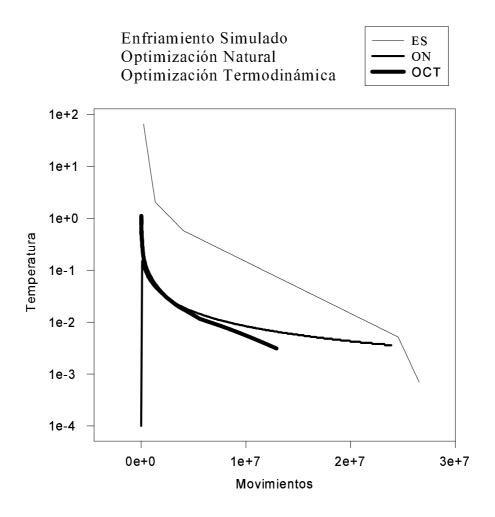

En el capítulo 3 se presenta el algoritmo de *Optimización Natural (ON)*, un método auto-sintonizable para el tratamiento de problemas de ubicación. Asimismo se proporcionan resultados experimentales comparándolo con el algoritmo de *Enfriamiento Simulado*.

En el capítulo 4, se presenta *OCT* (*Optimización Combinatoria Termodinámica*), un método nuevo de optimización combinatoria basado en principios termodinámicos, que se adapta automáticamente a distintos problemas y funciones de coste. Su efectividad se pone de manifiesto mediante comparaciones con una herramienta que utiliza el algoritmo de *Enfriamiento Simulado*.

En el capítulo 5 se profundiza en el problema de la congestión en FPGAs, y se desarrolla el modelo probabilístico *Valores Esperados de Ocupación (VEO)* para estimar la congestión local en la fase de ubicación. Se muestra la fiabilidad del modelo a través de un conjunto de resultados experimentales y se discute su ámbito de aplicación.

El capítulo 6 enlaza con la problemática del capítulo anterior y justifica un cambio de orientación en la aproximación a la solución del problema de la congestión local. Se presenta el algoritmo de cableado *Regiones de Steiner Rectilíneas (RSR)*, el cual es una aproximación polinómica a la solución del problema del *Árbol de Steiner Mínimo Rectilíneo (ASMR)*, y se compara con las mejores aproximaciones al *ASMR* desarrolladas hasta la fecha. Asimismo, se describe una estrategia de ubicación en etapas (*U-RSR*) facilitada por el algoritmo de *Optimización Combinatoria Termodinámica*, y cuyo objetivo es reducir la congestión local realizando medidas de la misma con el algoritmo *RSR*. Para terminar este capítulo, se presenta un algoritmo de cableado global basado en las regiones *RSR (CG-RSR)*, y se comparan los resultados producidos por la estrategia conjunta de ubicación y cableado (*UCG-RSR*), con la herramienta *Versatile Place&Route* (VPR) de la Universidad de Toronto.

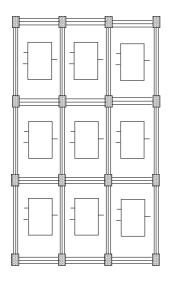

En el capítulo 7 se analizan las causas de la baja utilización de los recursos lógicos en los sistemas Multi-FPGAs. Se presenta un modelo para describir las mallas de FPGAs, y se realiza la formulación del problema de partición y ubicación dentro de ese modelo. Finalmente, se diseña una estrategia para obtener un buen compromiso *tiempo/calidad* para la resolución del problema basada en los algoritmos de *OCT* y *RSR* aplicándola a un conjunto de circuitos de prueba.

Por último, en el capítulo 8 se realiza una recopilación de las principales aportaciones de la tesis así como las futuras líneas de investigación a seguir.

# Capítulo 2

# Arquitectura de los sistemas reconfigurables y herramientas de diseño automático

# 2.1 Los sistemas reconfigurables

Los sistemas reconfigurables están proporcionando una gran flexibilidad para la producción de sistemas digitales. Las posibilidades que ofrecen los sistemas reconfigurables abren nuevos caminos como el prototipado rápido, la emulación lógica, las computadoras reconfigurables o el hardware multimodo. Podemos encontrar distintos tipos de circuitos reconfigurables [BR96] como son los SPLDs (Simple Programmable Logic Devices), los CPLDs (Complex Programmable Logic Devices) o las FPGAs (Field Programmable Gate Arrays). Los primeros en aparecer fueron los SPLD, que permiten implementar funciones lógicas en forma de suma de productos. Conforme la tecnología avanzó, se hizo posible la integración de varios SPLDs en un único chip constituyendo los CPLDs. Frente a estos dispositivos programables existían otros dispositivos lógicos de propósito general con una mayor capacidad de integración como son los arrays de puertas o MPGAs (Mask-Programmable Gate Arrays). Los MPGAs están formados por una matriz de transistores prefabricados cuyas conexiones se pueden configurar durante el proceso de fabricación del chip, dando lugar a un circuito específico. Con este panorama, aparecieron las FPGAs que proporcionaban un punto de encuentro entre ambas tecnologías. Así, las FPGAs surgieron originalmente con una doble identidad. Por una parte, se podían considerar MPGAs baratos, lentos y de baja densidad lógica. Por otra parte, eran como PLDs de elevado coste y mayor capacidad lógica. Las FPGAs son, por lo tanto, circuitos integrados que disponen de un conjunto de recursos lógicos y de interconexión prefabricados. El usuario sólo tiene que programarlos para darles una determinada funcionalidad. De esta forma, las FPGAs proporcionan dispositivos digitales de alta escala de integración configurables por el usuario. Tanto el tiempo como los costes de desarrollo se ven reducidos drásticamente. Existen básicamente dos tecnologías para la programación de las FPGAs: los antifusibles y las celdas de memoria SRAM. Las FPGAs de antifusibles no son reprogramables ni volátiles. Por el contrario, las FPGAs programables por celdas de memoria SRAM son volátiles y reprogramables. De aquí en adelante nos centraremos en estas últimas por ser las que mayor interés despiertan. Aunque la volatilidad de las SRAM-FPGAs fue considerada inicialmente como un gran inconveniente, con el tiempo ese defecto se ha convertido en su principal virtud. Puesto que son dispositivos reprogramables, su configuración se puede cambiar fácilmente para depurar diseños o poner al día los sistemas. Entre las aplicaciones típicas de las FPGAs se pueden citar: la lógica aleatoria, la integración de varios SPLDs en uno sólo, los dispositivos de control, los dispositivos de codificación y de filtrado en comunicaciones, y en general cualquier sistema de tamaño pequeño o mediano. Existe otra serie de aplicaciones que requieren mayor capacidad lógica, y por lo tanto, exigen la interconexión de varias FPGAs formando sistemas Multi-FPGAs. Entre estas aplicaciones están la generación de prototipos correspondientes a diseños sobre arrays de puertas, o la emulación y depuración de grandes sistemas hardware. De la misma forma, los sistemas basados en FPGAs se pueden utilizar con diferentes configuraciones en sistemas multimodo o computadoras reconfigurables. Otra aplicación emergente basada en FPGAs es el entrenamiento y ejecución de redes neuronales. A continuación profundizamos en estas y otras posibilidades que ofrecen las FPGAs en el diseño de sistemas digitales.

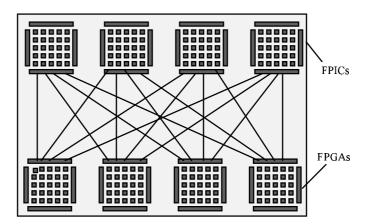

La emulación lógica de circuitos de aplicación específica (ASICs) [VBB93, DBTHHA94, WSKR99] es una de las aplicaciones de mayor éxito de los sistemas reconfigurables. Los diseños de ASICs deben ser verificados para asegurar que el circuito realiza sus funciones correctamente. Esta tarea tradicionalmente se ha realizado por simulación software de forma lenta. En emulación lógica, el circuito se implementa sobre un sistema formado por varias FPGAs (sistema Multi-FPGA). De esta forma, se puede acelerar la verificación del ASIC en varios ordenes de magnitud. Por otra parte, distintos procesadores [Gat95, Gan96] y arquitecturas [Mei95] también se están

emulando en sistemas Multi-FPGAs dada la versatilidad que proporcionan estos dispositivos.

De forma similar, los sistemas reconfigurables facilitan el desarrollo rápido de prototipos [BEKH94, KG95, MK98, KRWDP99], los cuales permiten, en algunos casos, realizar pruebas de integración de los componentes digitales a nivel de sistema incluso antes de su fabricación como circuito integrado [RBB91].

Otra área con gran futuro para las FPGAs son las computadoras reconfigurables [HWGG93, HKH94, Bax99, BR2000, SLLKBFM2000]. Estas computadoras estarán constituidas por procesadores y lógica programable de forma que podrán proporcionar hardware especializado para la aplicación que esté siendo ejecutada. Los beneficios que se pueden obtener son similares a los que ofrecen los procesadores con conjuntos de instrucciones diseñados para aplicaciones específicas (ASIP). Este tipo de procesadores permite acelerar la ejecución de las aplicaciones para los que están diseñados. Las computadoras reconfigurables obtendrán ese mismo beneficio sin necesidad de comprometer el hardware, de forma que se podrán adaptar a distintas aplicaciones.

Igualmente, el uso de sistemas reconfigurables hace que la supercomputación tenga un menor coste [Wau91, YNK96], y por tanto sea más accesible para todos los usuarios. La flexibilidad de las FPGAs permite explotar el paralelismo a niveles de bit, aritmético, de instrucción o de aplicación [CEA95, CW98, HBS98, WK99]. El potencial de las FPGAs en este campo ya se ha hecho evidente con el desarrollo de diferentes procesadores para investigación. Así, el sistema Splash [Gok90] configurado para la resolución de problemas de correspondencia de cadenas genéticas, considerablemente e1 rendimiento de otras implementaciones basadas supercomputadores. El sistema DECPeTLe-1, también es citado por sus aplicaciones y récords en distintas disciplinas como la criptografía [VBRSTB95], o la física de altas energías [MVB95]. Por otra parte, se diseñan aceleradores hardware para aplicaciones concretas, como es la simulación de la dinámica de n cuerpos [CKL95], o coprocesadores para criptografía [PT98] y procesamiento vectorial [AM98]. Asimismo, se han realizado distintas implementaciones basadas en FPGAs de algoritmos genéticos para la resolución de problemas de optimización [GN96, BM98, KBHBKA98, SMP99, HZ2000]. También,

se han propuesto otros modelos basados en FPGAs para reducir los tiempos de computo en la resolución de problemas diversos como el cálculo de órbitas de satélites [BS98], o problemas de física estadística [MI93, MC93].

Los sistemas reconfigurables también presentan un futuro interesante en sectores como el de las comunicaciones [CME93, MGTG97, TBD98], los dispositivos multimedia [EWJ95, MO98] o sistemas de vídeo [LADDRSS98, PWH99, MKBGHS2000]. Por una parte, las FPGAs permiten salvar las restricciones de área que imponen algunas de estas aplicaciones, posibilitando el diseño de interfaces reconfigurables más versátiles [RPM91, SRR98]. Por otra parte, el paralelismo potencial de las FPGAs puede proporcionar el elevado rendimiento computacional necesario para el procesamiento digital de las señales (DSP) requerido en muchas de estas aplicaciones [BM94, Sch95, KVGO99]. Además, las FPGAs permiten una rápida actualización de los productos, la cual es imprescindible en estas áreas debido a sus continuos avances. También se empiezan a describir aplicaciones DSP con FPGAs en otras áreas de conocimiento como la visión artificial [KDCA96, WH97, AP99], el reconocimiento del habla [YSS97], el radar [MM99] o el sonar [GN98].

Otro de los campos donde las FPGAs despiertan especial interés es el de las redes neuronales [DHY93, BH94, BT95, PDBS98]. Las redes neuronales son modelos computacionales basados en la estructura de las neuronas del cerebro. Uno de los aspectos más importantes de estos modelos es que los elementos básicos que componen la red se configuran para cada problema mediante un proceso de *aprendizaje*. Las posibilidades de reconfiguración que ofrecen las FPGAs pueden facilitar este proceso de aprendizaje debido que la configuración hardware se puede modificar en todo momento.

En este mismo sentido, aparecen nuevas técnicas agrupadas bajo el nombre de reconfiguración dinámica [Tud95, JTYCS98, MMFC98]. Entre otras posibilidades, la reconfiguración en tiempo de ejecución permitiría disponer de un hardware virtual equivalente a la memoria virtual disponible en las computadoras actuales [LD93, LS96, Wer97, BDHSW97, MDGS98, ML99]. Es decir, la reconfiguración permite ahorrar hardware reutilizando el mismo recurso con distintas configuraciones.

Hasta aquí, se ha mostrado una revisión de algunas de las aplicaciones actuales de los sistemas reconfigurables. También se han mencionado algunas líneas de investigación que previsiblemente orientarán las futuras aplicaciones de los sistemas basados en FPGAs. Sin embargo, para hacer realidad todo este potencial que presentan las FPGAs, es necesario el desarrollo de herramientas automáticas que permitan el tratamiento, de forma eficiente, de la complejidad creciente de los circuitos. Como veremos a continuación, de acuerdo con el actual ciclo de diseño VLSI, es en la etapa de diseño físico cuando se realiza la correspondencia entre la representación del circuito y el dispositivo físico final que lo soporta. En el caso de las FPGAs, este proceso se realiza habitualmente descomponiendo el circuito en subcircuitos o bloques, de forma que la funcionalidad de cada bloque se corresponda con la que se puede proporcionar mediante la configuración de un bloque de lógica prefabricado. En una segunda fase, se realiza la ubicación o correspondencia entre bloques lógicos y físicos de acuerdo con algún criterio de proximidad. Finalmente, la comunicación entre subcircuitos relacionados, se establece configurando los recursos de cableado programables distribuidos a lo largo y ancho de toda la FPGA. La programación de una FPGA lleva asociadas, por lo tanto, una serie de tareas complejas cuya realización óptima requiere la resolución de distintos problemas de optimización combinatoria, los cuales resultan inabordables sin la ayuda de computadoras. De esta forma, la automatización se convierte no sólo en un apoyo, sino en un objetivo irrenunciable.

En las siguientes secciones se introducen las ideas básicas relativas al diseño *VLSI* (*Very Large Scale Integration*), y a las distintas metodologías o estilos de fabricación. Seguidamente, se repasa el estado de la tecnología de las FPGAs a través de las diferentes familias de dispositivos que proporcionan los distintos fabricantes. Asimismo, se realiza una revisión general de los elementos que componen las FPGAs centrándonos, de manera más detallada, en aquellos elementos que son relevantes para la descripción de los problemas planteados en este trabajo de investigación. Ese mismo tratamiento se dará a los sistemas Multi-FPGA. Finalmente, se exponen los problemas derivados del diseño físico orientado a FPGAs y sistemas Multi-FPGA, y se analizan las

virtudes y defectos de los procedimientos y herramientas desarrollados hasta la fecha para su resolución.

### 2.2 Ciclo de diseño VLSI

El ciclo de diseño de circuitos de muy alta escala de integración o *VLSI*, comprende una serie de etapas que van desde la especificación de los requisitos que debe cumplir el circuito integrado al producto final, es decir, al chip empaquetado. Entre estas dos fases podemos distinguir una serie de pasos a los que se les denomina *ciclo de diseño VLSI*. De acuerdo con [She99], este ciclo se compone de las siguientes etapas:

- 1. Especificación del sistema: La especificación del sistema normalmente recoge un compromiso entre los requisitos del mercado, la tecnología y la viabilidad económica del producto. Las especificaciones deben incluir la funcionalidad, la velocidad, la potencia y las dimensiones físicas del chip.

- 2. Diseño de la arquitectura: A partir de las especificaciones, en esta etapa se diseña la arquitectura del sistema. Este diseño incluye decisiones relativas a las instrucciones que ejecutará el sistema, al grado de paralelismo espacial y temporal, a la jerarquía de memoria, etc. El resultado de este diseño es una descripción en forma de texto denominada Especificación de la Micro-Arquitectura o MAS (Micro-Architectural Specification). En este documento se debe incluir una predicción de la velocidad, potencia y tamaño del circuito integrado.

- **3. Diseño funcional o de comportamiento:** En esta etapa se identifican las unidades funcionales del sistema y sus requisitos de interconexión. Se describe el comportamiento de cada unidad funcional mediante sus entradas, salidas y tiempo, sin especificar la estructura interna. El resultado del diseño funcional es una descripción que relaciona las distintas unidades funcionales, y permite la emulación del sistema entero para su depuración.

- **4. Diseño lógico:** En la etapa de diseño lógico se derivan, a partir de la descripción de comportamiento, las operaciones aritméticas y lógicas, el flujo de control, el tamaño de las palabras y la asignación de registros. El resultado se denomina descripción a nivel de transferencia de registros (*RTL-Register Transfer Level*), y se expresa habitualmente en un lenguaje de descripción de hardware (*HDL- Hardware Description Language*) como *VHDL o Verilog*. La descripción *RTL* está formada por expresiones booleanas e información de tiempo, y se puede utilizar para simulación y verificación. En esta etapa, las expresiones booleanas se optimizan de acuerdo con los objetivos de área, tiempo, potencia, etc. En ocasiones, el paso de la descripción funcional a *RTL* se puede automatizar por medio de herramientas de síntesis de alto nivel (*High Level Synthesis*).

- **5. Diseño del circuito:** Durante esta etapa, las expresiones booleanas se convierten en una representación del circuito, teniendo en cuenta los requisitos de potencia y velocidad. La representación del circuito se le suele denominar lista de redes *(netlist)*, y contiene los distintos elementos (macros, puertas, etc.) y sus interconexiones. Mediante la simulación del circuito en este nivel se pueden verificar su correcto funcionamiento. Las herramientas de síntesis lógica permiten generar automáticamente la *netlist* a partir de la descripción *RTL*.

- **6. Diseño físico:** En la fase de diseño físico, la representación circuital o *netlist*, se transforma en una representación geométrica del circuito denominada composición (*layout*). Durante la fase de diseño físico, los componentes lógicos se transforman en *patrones geométricos*, de acuerdo con las reglas de diseño dictadas por la tecnología y el proceso de fabricación. Las interconexiones entre componentes normalmente se realizan, utilizando diversas capas, a través de regiones dedicadas. En esta etapa, también se realizan distintas verificaciones del diseño.

- **7. Fabricación:** Una vez verificado el diseño, los datos de la composición se mandan a fabricar. En el proceso de fabricación, los datos correspondientes a las distintas capas de la composición se transforman en máscaras fotolitográficas. El proceso de fabricación

se realiza en varias etapas durante las cuales se depositan y difunden, a través de las máscaras, diversos materiales sobre la oblea de silicio. Dependiendo del tamaño del circuito integrado, con una oblea de 20cm o 30cm de diámetro se pueden fabricar varios chips.

**8. Empaquetado, prueba y depuración:** En la última etapa la oblea se trocea en chips individuales. Los chips utilizados en placas de circuitos impresos (*PCB-Printed Circuit Board*) se empaquetan y se prueban para asegurar que cumplen las especificaciones, mientras que los chips diseñados para Módulos Multi-Chip (*MCM- Multi-Chip Modules*) no se empaquetan al ser integrados directamente en una plataforma mayor.

#### 2.3 Estilos de diseño físico

El ciclo de diseño físico [She99] es un proceso complejo por lo que normalmente se divide en varias etapas. Para manejar la dificultad del diseño físico han surgido unos pocos *estilos* que responden a distintas filosofías de diseño, costes y tiempos de puesta en el mercado (*time-to-market*). Entre esos estilos podemos citar: *FC* (*Full-Custom*), *SC* (*Standard Cell*), *GA* (*Gate Arrays*), *FPGA* (*Field Programmable Gate Arrays*) y *SG* (*Sea of Gates*).

El estilo FC permite mezclar patrones geométricos correspondientes a bloques funcionales de distintos tamaños. La partición del circuito en bloques funcionales se realiza habitualmente de forma jerárquica. Debido a su complejidad, se suele utilizar en la fabricación de microprocesadores donde prima la calidad sobre tiempo de diseño.

En el estilo *SC* se recurre a una biblioteca de celdas standard (500-2000 unidades) para realizar la composición, donde cada celda está caracterizada por su funcionalidad y rendimiento. El circuito se divide en bloques de forma que cada uno sea equivalente a una celda predefinida. Las celdas son rectangulares, de la misma altura, y se disponen en filas dejando canales intermedios entre las filas para el cableado. La complejidad del diseño físico se reduce respecto al estilo *FC*. El estilo *SC* es inherentemente no jerárquico por lo que se utiliza principalmente en lógica aleatoria y de control. Salvada

la inversión inicial en el desarrollo de la biblioteca de celdas, el diseño en SC es más rápido que en FC sin alcanzar el rendimiento ofrecido por este último. El estilo SC se ajusta mejor a circuitos de tamaño moderado y volúmenes de producción medios.

En el estilo *GA* existe un array de celdas prefabricadas de igual tamaño (puertas lógicas), separadas por canales horizontales y verticales para el cableado. El circuito se modifica de forma que se pueda dividir en bloques idénticos, en un número menor o igual que el número de puertas disponibles. La ventaja de este estilo de diseño es que sólo las últimas etapas del proceso de fabricación dependen del circuito diseñado. Por esta razón, la fabricación de un circuito con esta tecnología es más barata.

De forma similar a los GA, las FPGAs están formadas por un array de celdas prefabricadas separadas por canales horizontales y verticales para el cableado. La ventaja de las FPGAs sobre los GA es que esas celdas, normalmente de mayor complejidad, son programables por el usuario. Además, la mayoría de las FPGAs no sólo son programables, sino que se pueden reprogramar con las innumerables ventajas que esto conlleva. Como contrapartida frente a los GA, el nivel de integración en las FPGAs es menor, y los tiempos de retardo mayores.

Por último, el estilo SG mejora a los GA en el nivel de integración debido a que todo el área del circuito integrado está llena de transistores. El cableado se realiza utilizando puertas lógicas con lo que se pierde efectividad en área, o añadiendo más capas para conexiones en el circuito integrado, lo que encarece el tiempo y coste de fabricación. En el resto del capítulo nos centraremos en el estilo de diseño de FPGAs, el cual es el objeto de esta tesis.

#### 2.4 Familias de FPGAs

Las FPGAs son dispositivos de lógica programable inicialmente orientados a Circuitos de Aplicación Específica (ASICs- Application Specific Circuits), debido a que permiten reducir drásticamente el tiempo de puesta en el mercado de estos dispositivos.

En la actualidad, la capacidad de las FPGAs está por encima del millón de puertas lógicas lo que permite pensar en el desarrollo de sistemas digitales enteros integrados en estos dispositivos programables. Existen diferentes familias de FPGAs reconfigurables

como son las Xilinx [Xil], Altera[Alt], Lucent Orca [Luc] y Actel [Act]. Una característica común a casi todas estas familias, es el uso de LUT#s (Look-Up Tables) para la generación de cualquier función lógica de # entradas. El número de entradas por LUT puede variar de unas FPGAs a otras, siendo 4 o 5 valores habituales. En cuanto a la estructura de los bloques lógicos o celdas básicas, sí se encuentran diferencias significativas de unas familias a otras. En la Tabla 2.1 se reproduce un estudio reciente [KS2000] donde se muestra las características principales de estas familias como son: capacidad del mayor dispositivo disponible de la familia, tipo y número de bloques lógicos o celdas básicas, número de pines de entrada/salida y tecnología de fabricación. En la Tabla 2.2 se muestra una comparación de la capacidad de estos dispositivos medida en puertas lógicas.

Tabla 2.1 Familias de FPGAs

| Familia          | Dispositivo | Bloque | Capacidad      | Entrada/ | Tecnología    |

|------------------|-------------|--------|----------------|----------|---------------|

|                  | mayor       | Lógico | Celdas básicas | Salida   |               |

| Xilinx 4000      | XC40250XV   | CLB    | 8,464 CLBs     | 448      | SRAM (0.25μ)  |

| Xilinx Virtex,   | XVC3200E    | CLB    | 16,000 CLBs    | 804      | SRAM (0.18μ)  |

| Virtex-E         |             |        |                |          |               |

| Altera FLEX 8000 | 81500       | LE     | 1,296 LEs      | 208      | SRAM (0.5μ)   |

| Altera FLEX 10k  | EPF10K250   | LE     | 12,160 LEs     | 470      | SRAM (0.25μ)  |

| Altera Apex20k   | EP20K1500K  | LE     | 51,840 LEs     | 808      | SRAM (0.18μ)  |

| Actel ProAsic    | A500K510    | tile   | 51,200 tiles   | 623      | Flash (0.25µ) |

| Lucent ORCA      | OR3L225B    | LUT    | 11,552 LUTs    | 612      | SRAM (0.25μ)  |

**Tabla 2.2** Capacidad lógica de las distintas familias de FPGAs

| Familia         | Dispositivo | Celdas lógicas (LC) por | Capacidad      | Capacidad     |

|-----------------|-------------|-------------------------|----------------|---------------|

|                 | mayor       | Bloque lógico           | Puertas eq.    | Puertas       |

|                 |             | (1)                     | (lógica y RAM) | (sin memoria) |

| Xilinx 4000     | XC40250XV   | 2.375                   | 250,000        | 241,000       |

| Xilinx          | XVC3200E    | 4.5                     | 4,074,387      | 876,096       |

| Virtex-E        |             |                         |                |               |

| Altera FLEX 800 | 81500       | 1                       | 16,000         | 16,000        |

| Altera FLEX 10k | EPF10K250   | 1                       | 250,000        | 149,000       |

| Altera Apex20k  | EP20K1500K  | 1                       | 1,500,000      | 622,000       |

| Actel ProAsic   | A500K510    | 0.4                     | 410,000        | 240,000       |

| Lucent ORCA     | OR3L225B    | 1                       | 340,000        | 166,000       |

<sup>(1)</sup>  $Celda\ l\'{o}gica(LC) \sim LUT4 + FF\ (Definici\'{o}n\ introducida\ por\ Xilinx\ [Xil]\ para\ la\ comparaci\'{o}n$  entre distintas tecnologías)

Analizando las tablas 2.1 y 2.2, se observa que el número de celdas básicas varía con la granularidad. La celda básica en Xilinx es el CLB. Sin embargo, la estructura de un CLB es diferente en las familias XC4000 y Virtex. Así, un CLB de la familia XC4000 contiene 2 LUT4 (Look-up table), 1 LUT3 y 2 FFs, mientras que un CLB de la familia Virtex está compuesto de dos partes, donde cada una de ellas contiene 2 LUT4s, 2 FFs (*Flip-Flops*) y multiplexores. En Altera, el bloque básico es el LE (Logic Element), que contiene 1 LUT4 y 1 FF. Las FPGAs Actel ProAsic tienen una granularidad más fina con celdas denominadas *tile*, las cuales se pueden configurar como funciones de tres entradas o como FFs. Por último, las FPGAs Lucent Orca están basadas en LUT4s. Para hacer posible la comparación entre las distintas tecnologías, Xilinx introdujo la noción de Celda Lógica (LC), la cual consiste en 1LUT4+1FF (equivalente a 12 puertas). De esta forma, el CLB de la familia XC4000 es 2.375 LCs y el de la familia Virtex es de 4.5 LCs. El *tile* de la familia Actel equivale a 0.4 LCs. En la Tabla 2.2 también se muestra una estimación de puertas equivalentes determinada a partir de los datos proporcionados por los fabricantes.

## 2.5 Arquitectura de las FPGAs

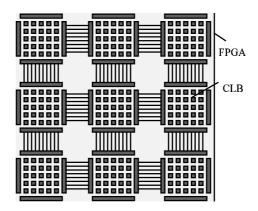

En la sección anterior, se ha realizado una revisión de las distintas FPGAs disponibles en el mercado. Se destacó asimismo la estructura de las celdas básicas como elemento diferencial entre todas ellas. Existen también diferencias en cuanto a la disposición de estas celdas en la FPGA. Además, las FPGAs de última generación empiezan a incorporar nuevos elementos como interfaces para la conexión de memorias externas (*megabytes*), que sumados a nuevos bloques de memoria (*kilobytes*), y a las tradicionales unidades de memoria distribuidas a lo largo y ancho de toda la matriz de celdas básicas (*bytes*), permiten hablar de organizaciones jerárquicas de memoria. Además, aparecen nuevos elementos para el tratamiento aritmético y la sincronización interna/externa del tiempo. A pesar de las particularidades que ofrecen las distintas familias, también existe una característica común a casi todas ellas como es la organización básica de celdas en filas y columnas. A partir de esa disposición de los bloques lógicos, los recursos programables de propósito general para la interconexión

entre celdas, se disponen normalmente formando canales horizontales y verticales. Al no existir una única arquitectura de FPGAs, las herramientas comerciales para el diseño físico sobre estos dispositivos, tienen en consideración las características particulares de cada familia. Con el objetivo de hacer posible la comparación directa entre herramientas, es habitual en la literatura la presentación de resultados del diseño físico realizado sobre una arquitectura de tipo *array de celdas* [BRV92, LB93, CLWL95, AR96, LW97, WM97, BR97, ACGR98], la cual integra aquellas características que son comunes a la mayoría de las FPGAs. A continuación pasamos a describir los elementos básicos que componen esta arquitectura.

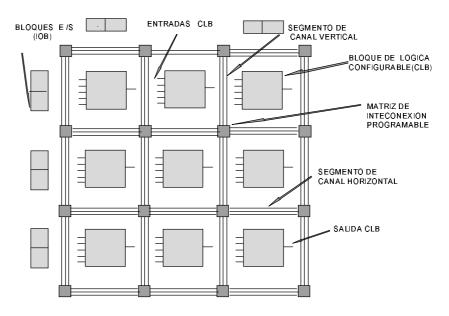

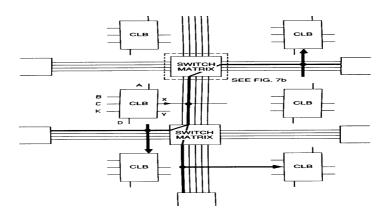

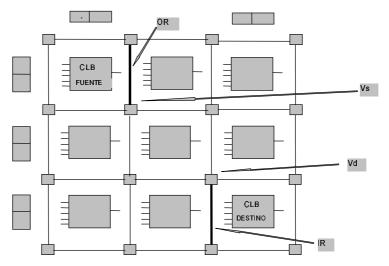

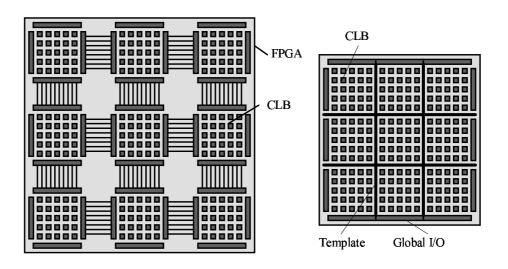

La estructura básica de una FPGA como la de la Figura 2.1 está constituida por una matriz de bloques lógicos configurables (CLBs), cuyos elementos están separados por segmentos de canal horizontales y verticales. En la periferia de la matriz se dispone un conjunto de bloques programables de entrada/salida (*IOBs-Input/Output Blocks*) para la comunicación con el exterior.

Figura 2.1 Elementos básicos que componen una FPGA

Los CLBs son la unidad lógica básica de esta FPGA. Cada CLB se compone de una serie de entradas, salidas y lógica combinacional programable, que permite la

configuración de cualquier función lógica de sus entradas. Asimismo, dispone de elementos de almacenamiento para la implementación de circuitos secuenciales. La estructura interna de los CLBs depende del tipo de FPGA, proporcionando más o menos funcionalidad según sus componentes.

Por otra parte, las FPGAs proporcionan recursos de cableado para la interconexión de las redes que componen el circuito. Entre los canales que forman los elementos de la matriz de CLBs se encuentran los recursos de interconexión de propósito general. Éstos se componen de segmentos de canal y elementos de interconexión programables. Así, cada segmento de canal está compuesto por un conjunto de cables, los cuales desembocan en matrices de interconexión programables situadas en la intersección de los canales horizontales y verticales. Además, tanto a la salida como a la entrada de los CLBs se dispone de dispositivos programables para su interconexión con los cables del segmento de canal más cercano. La configuración de todos estos elementos programables permite el establecimiento de conexiones entre determinados CLBs. Otros recursos de cableado consisten en conexiones directas entre CLBs vecinos, y líneas largas normalmente utilizadas para la interconexión de las redes globales.

Por último, los IOBs proporcionan la frontera entre la lógica interna de la FPGA y los terminales externos del circuito integrado. Los IOBs pueden ser configurados como terminales de entrada o de salida de acuerdo con las necesidades del circuito que se está implementando.

.

#### 2.6 Diseño físico sobre FPGAs

Una parte importante en el diseño de circuitos orientado a FPGAs es el diseño físico. Como ya vimos, el diseño físico [She99] es una etapa del ciclo de diseño de circuitos VLSI [Mich94]. En esta etapa, la representación circuital de los componentes del sistema se transforma en una representación geométrica. En el caso de las FPGAs, este ciclo consiste en la implementación de la lista de redes del circuito mediante los elementos programables, tanto lógicos como de interconexión, de la FPGA. Este proceso se lleva a cabo habitualmente en tres etapas: partición, ubicación y cableado.

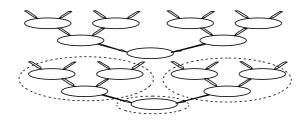

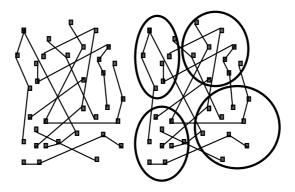

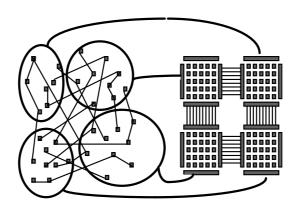

Mediante la partición (Figura 2.2), el circuito se divide en bloques de forma que la funcionalidad de cada bloque se pueda implementar con un único CLB, que es la unidad lógica básica de las FPGAs [HOIW94][Sas93]. El problema de la partición orientada a FPGAs [MBS95], es sustancialmente distinto del problema de partición dirigida a otros estilos de diseño. En el caso de las FPGAs, el problema de la partición depende fundamentalmente de la arquitectura de los CLBs con los cuales se va a implementar la lógica del circuito. Por ejemplo, la partición orientada a CLBs que contienen LUTs debe realizarse de forma que el resultado sea un conjunto de funciones lógicas, de cuatro o cinco entradas, sintetizables mediante estos dispositivos.

Figura 2.2 Partición del circuito en CLBs lógicos

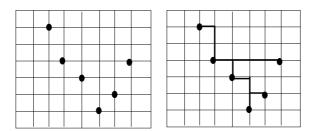

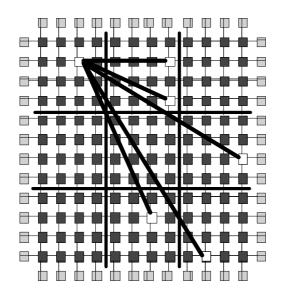

La segunda etapa del ciclo de diseño físico orientado a FPGAs es la ubicación. En la fase de ubicación, los bloques lógicos (CLBs lógicos) obtenidos mediante la partición del circuito se asignan a localizaciones físicas concretas (CLBs físicos) sobre la matriz de CLBs de la FPGA (Figura 2.3).

Figura 2.3 Ubicación de CLBs lógicos en CLBs físicos

Una vez optimizada la ubicación la siguiente etapa es el cableado, el cual consiste en la conexión de los CLBs físicos relacionados (redes del circuito), mediante la programación de los recursos de interconexión de la FPGA. A continuación pasamos a describir más detalladamente los procesos de ubicación y rutado objeto de este trabajo.

#### 2.6.1 Ubicación sobre FPGAs

La etapa de ubicación es un paso clave en el ciclo de diseño físico al afectar al área y a la velocidad de los circuitos. El problema de la ubicación sobre FPGAs, aún siendo similar a la ubicación sobre arrays de puertas y celdas standard, presenta algunas peculiaridades. En los arrays de puertas y celdas standard, el retardo de las señales debido al cableado proviene únicamente de la distancia que tiene que viajar la señal entre los nodos que se interconectan. Sin embargo, el cableado del circuito sobre las FPGAs se realiza por medio de la interconexión de segmentos de cable a través de interruptores programables [RGS93], los cuales provocan en las señales un retardo mayor que el que se produce en los arrays de puertas y celdas standard. Por lo tanto, el retardo producido en las señales por el cableado sobre FPGAs, es más sensible a la ubicación que en otros dispositivos. Por otra parte, el número de cables por segmento de canal en una FPGA es fijo, de forma que aquellos circuitos que durante el cableado no se ajusten a la capacidad limitada de los segmentos de canal, no se podrán implementar en esa FPGA.

El problema de la ubicación sobre una FPGA se puede especificar como: dado un circuito compuesto de un número fijo de bloques de lógica, bloques de entrada/salida, y de la lista de interconexiones entre estos bloques, asignar posiciones para cada bloque sobre la matriz de CLBs e IOBs de la FPGA, de forma que todas las redes se puedan rutar con los recursos de cableado disponibles. La fase de ubicación tiene una gran influencia sobre la cantidad de cable o recursos de interconexión necesarios para rutar el circuito. Como consecuencia, optimizar la ubicación para el ahorro de cable debe ser un objetivo primordial en el diseño físico. Otro objetivo que frecuentemente se plantea en la fase de ubicación es la minimización del retardo total del circuito. La consecución de

cualquiera de estos objetivos exige realizar una selección de soluciones entre todas las ubicaciones posibles. De manera que, por una parte tenemos que cuantificar los objetivos mediante una función de coste que permita la discriminación entre las distintas soluciones. Por otra parte, y dado que el número de soluciones crece considerablemente con el tamaño del problema, una exploración adecuada del espacio de soluciones exige el uso de algoritmos de optimización combinatoria. En las siguientes subsecciones, revisamos las principales funciones de coste y algoritmos que constituyen el estado del arte de la ubicación. Asimismo, señalamos algunos puntos débiles de estas funciones y algoritmos susceptibles de mejora.

#### Funciones de coste

Como ya se ha comentado, el principal objetivo de la fase de ubicación es proporcionar una colocación de los bloques lógicos de forma que se facilite el cableado. Por lo tanto, la función de coste en esta etapa debe predecir, para una ubicación dada, la cantidad de cable que será necesaria para rutar el circuito. De forma general, esa cantidad de cable dependerá de la herramienta de cableado utilizada. Sin embargo, sí es posible hacer una primera estimación suponiendo que el cableado de todas las redes se realizará por el camino más corto, lo cual es bastante razonable. El cálculo de las longitudes de una red de dos terminales normalmente se realiza utilizando la distancia rectilínea o de Manhattan. La distancia Manhattan entre dos puntos de coordenadas (x1,y1), (x2,y2) se define como:

$$L=|x_1-x_2|+|y_1-y_2| \tag{2.1}$$

Así, podemos descomponer las redes multiterminal en redes de dos terminales, y medir la distancia entre todos los pares fuente/destino (L<sub>i</sub>), obteniendo de esta forma la longitud de cable total del circuito. La Ecuación 2.2 muestra la función de coste *longitud de cable total*.

$$\cos te = \sum_{i \in redes} L_i \tag{2.2}$$

En algunos métodos de ubicación analíticos se han utilizado funciones de coste cuadráticas [Hall70, AJK82] de la forma dada por la Ecuación 2.3.

$$Coste = \sum_{i \in redes} L_i^2 \tag{2.3}$$

Sin embargo, se ha observado experimentalmente que esta función mide de forma menos precisa la futura demanda de cable que la función lineal [SDJ91]. Por otra parte, aunque la función lineal dada por la Ecuación 2.2 mide la longitud de cable requerido para redes de dos terminales, ésta pierde precisión según aumenta el número de nodos en redes multiterminal. Como se verá en el capítulo 5, la métrica denominada del *semiperimetro* constituye una estimación mejor de la futura demanda de cable correspondiente a una ubicación dada. El *semiperimetro* estima la longitud de cable necesario para rutar una red multiterminal por la mitad del perímetro del área que la engloba. Por lo tanto, aplicado a todas las redes (Ecuación 2.4), el semiperímetro es una medida del cable total necesario para rutar el circuito. Su minimización permite reducir tanto la congestión global como los retardos de propagación producidos en las señales. Se debe resaltar que ahora, el conjunto de *redes* de la Ecuación 2.4, se refiere al conjunto de redes multiterminal sin descomponerlas en redes de dos terminales.

$$Coste = \sum_{i \in redes} semiperimetro_i$$

(2.4)

El semiperímetro también se denomina a veces *Bounding-Box*. Aquí, con el objeto de seguir la notación utilizada en [BR97], denominaremos *Bounding-Box* a la función de coste dada por la Ecuación 2.5, donde se realizan correcciones a la subestima de área de las redes multiterminal calculada con el *semiperímetro*.

$$Coste = \sum_{n=1}^{N_{nets}} \frac{q(n)}{C_{ay}} \left[ bb_x(n) + bb_y(n) \right]$$

(2.5)

Los términos  $bb_x$  y  $bb_y$  de la Ecuación 2.5 denotan respectivamente los límites horizontal y vertical de la caja que envuelve la red n, q(n) es un factor que compensa la subestima del área de las redes multiterminal [Che94], y  $C_{av}$  es la capacidad promedio de un canal en número de pistas. La función de coste *Bounding-Box* será utilizada posteriormente en esta tesis para realizar comparaciones entre los algoritmos de optimización combinatoria, ya que proporciona una estimación rápida y aceptable de la demanda de cable total.

Como hemos señalado anteriormente, la minimización del cable total necesario para rutar el circuito, consigue reducir la congestión global y los retardos en las señales de forma general, pues reduce el camino que tienen que recorrer las señales. Sin embargo, las métricas basadas en la longitud de cable, también pueden generar ubicaciones de los bloques lógicos que provoquen una demanda intensiva de los recursos centrales de interconexión durante el cableado, produciendo congestión en estas zonas [Cro95]. Es necesario, por lo tanto, la investigación sobre nuevas métricas que durante la fase de ubicación realicen estimaciones, y equilibren, las necesidades de cable por segmento de canal [EMHB95]. Se han publicado algunas funciones de coste guiadas por este objetivo [CP86]. En [CP86] se penaliza las ubicaciones en las que se prevé que se va a producir congestión durante el cableado mediante la siguiente función de coste:

$$\sigma = \frac{1}{2} \sum_{i \in redes} longitud(i) + \sum_{i \in Canal\ H} h_i^{2} + \sum_{i \in Canal\ V} v_i^{2}$$

(2.6)

donde

$$h_{i}' = \begin{cases} h_{i} - h_{avg} - h_{sd} & si \quad h_{i} > h_{avg} - h_{sd} \\ 0 & en \ otros \ casos \end{cases}$$

$$v_{i}' = \begin{cases} v_{i} - v_{avg} - v_{sd} & si \quad v_{i} > v_{avg} - v_{sd} \\ 0 & en \ otros \ casos \end{cases}$$

y donde  $h_i$  ( $v_i$ ) es el número de redes que cortan el canal horizontal (vertical) i,  $h_{avg}$  ( $v_{avg}$ ) es la media de  $h_i$  ( $v_i$ ), y  $h_{sd}$  ( $v_{sd}$ ) es la desviación standard de  $h_i$  ( $v_i$ )

Analizando la expresión, observamos que esta función de coste penaliza el exceso de cortes producidos en un segmento de canal determinado, bien horizontal o vertical. Sin embargo, la penalización se realiza a nivel de canal lo cual asegura que ningún canal soporte un exceso de conexiones, pero no asegura lo mismo para los segmentos de canal.

Otra forma más directa de afrontar el problema de la congestión consiste en una ubicación y rutado simultáneos. Con este método, en cada ubicación se puede medir la ocupación producida en cada segmento de canal mediante un cableado rápido, evitando de esta forma la congestión. Un ejemplo de esta orientación aparece en [NR98], donde se realiza una ubicación y rutados simultáneos. En cada ubicación explorada con un algoritmo de mejora iterativa, se actualiza el cableado de las redes afectadas. Sin embargo, la lentitud de las herramientas de cableado desarrolladas hasta la fecha hace poco viable esta aproximación. Como el autor de este artículo lamenta, la falta de algoritmos de cableado constructivos, le obligó a utilizar un algoritmo de tipo *laberinto*. Como veremos posteriormente, este tipo de algoritmos realizan muchas exploraciones innecesarias, resintiéndose la velocidad de proceso. Por otra parte, la función de coste utilizada en este trabajo es

$$Coste = W_r x R + W_r x T \tag{2.7}$$

donde R es el número de redes que impiden completar el cableado del circuito, T es el retardo del camino crítico actualizado mediante un análisis,  $W_r$  y  $W_t$  son pesos para normalizar los diferentes términos de la función de coste. Además de los problemas de lentitud en la actualización del cableado comentados anteriormente, este algoritmo de ubicación y rutado simultáneos pierde efectividad con la función de coste dada por la Ecuación 2.7. En esta función de coste no existe una medida o estimación directa del cable necesario para rutar el circuito, por lo que se pierde capacidad de discriminación entre soluciones. Así, la función de coste no distingue entre dos ubicaciones a las que les falte el mismo número de redes por cablear (R), pero que tengan distintas demandas

de cable. Sin embargo, es muy probable que sea más beneficiosa aquella ubicación que hasta el momento haya demandado menos cable.

### Algoritmos de ubicación

La ubicación es un problema NP-completo. Esta complejidad hace que sea conveniente la utilización de algoritmos probabilísticos para aproximarnos a la solución óptima. Dada la gran cantidad de posibles soluciones exploradas por estos algoritmos, el tiempo de cómputo necesario para determinar la calidad de las ubicaciones se convierte en un factor clave. Precisamente, una de las grandes ventajas de la métrica del semiperímetro como función de coste es su sencillez y rapidez de cálculo. Durante las últimas décadas, y debido al continuo incremento de la densidad de integración de los circuitos, se ha intensificado la investigación en los algoritmos de ubicación. Existe una serie de algoritmos que simulan fenómenos de la naturaleza como son: Dirigido por Fuerzas, Enfriamiento Simulado, Simulación de la evolución o Algoritmos genéticos. Otros, están basados en técnicas de partición como el algoritmo de Corte-mínimo, o técnicas de agrupamiento como el Crecimiento de Clusters. Finalmente, podemos destacar algoritmos analíticos como la programación lineal o la programación cuadrática. A continuación vemos una breve descripción de los más destacados.

El algoritmo *Dirigido por Fuerzas* [Qui75] simula un sistema de cuerpos enlazados por muelles. Es decir, aquellos bloques que están conectados por redes se supone que ejercen fuerzas atractivas entre ellos. La magnitud de estas fuerzas es directamente proporcional a la distancia entre los bloques. Si los bloques se dejarán libres, éstos se moverían hasta alcanzar una situación de equilibrio. Es decir, la solución para la ubicación de los bloques es aquélla en que el sistema alcanza el equilibrio. Por lo tanto, para calcular la posición de los bloques se plantean las ecuaciones de las fuerzas que intervienen en el sistema, y se resuelven utilizando los mismos métodos que se aplican a la mecánica clásica.

El algoritmo de Simulación de la Evolución [CP86] es similar al proceso natural de adaptación de las especies al entorno. El algoritmo comienza con un conjunto de configuraciones iniciales para la ubicación. Este conjunto de configuraciones iniciales

se generan de forma aleatoria y se les denomina población. Los individuos de la población consisten en cadenas de símbolos que representan posibles soluciones para el problema de la ubicación. El valor de los individuos se establece de acuerdo con una función de coste que estima su calidad. La población evoluciona mediante un proceso iterativo de generación en generación. En cada iteración se evalúa el coste de los individuos, y de acuerdo con su calidad, se asignan a los individuos probabilidades para ser seleccionados como padres. Mediante la aplicación de los operadores cruce y mutación sobre los padres seleccionados, se generan los nuevos individuos denominados descendencia. Los individuos que componen la descendencia se evalúan, y pasan a competir por la supervivencia con el resto de individuos de forma que el tamaño de la población permanece constante. La selección de los individuos basada en el coste, hace que los individuos de la población *mejoren* de generación en generación. Una de las claves para el éxito de los algoritmos evolutivos en la ubicación, es el diseño de un operador de cruce que sea rápido, y que tras su aplicación, no exija rehacer todo el cálculo de la función de coste. Esta dificultad, junto con la existencia de varios parámetros que necesitan ser ajustados para el buen funcionamiento del algoritmo, hace que existan pocas implementaciones de los algoritmos evolutivos aplicados a la resolución del problema de la ubicación.

En los algoritmos de ubicación basados en el *Corte-Mínimo* [Bre77], se realizan sucesivamente particiones del circuito en dos subcircuitos, minimizando el número de redes que pertenecen a las dos particiones simultáneamente. Por otra parte, en cada nivel de particionamiento, el área disponible del circuito integrado se divide alternativamente mediante líneas horizontales y verticales en dos subsecciones. En cada etapa de particionamiento, se asocian los subcircuitos con subsecciones. El proceso se repite hasta que cada subcircuito se compone de un sólo bloque lógico y tiene una posición definida. Entre las herramientas orientadas a FPGAs que utilizan esta técnica, podemos destacar la herramienta Altor [RSV85].

En las técnicas de *Crecimiento de Clusters* se parte de la ubicación de un bloque *semilla*. En cada iteración, se selecciona un bloque que esté fuertemente relacionado con los ya ubicados, y se sitúa cerca de ellos. La forma de selección, tanto del bloque

siguiente como de la posición donde éste se ubicará, hacen que el algoritmo genere soluciones de mayor o menor calidad, en más o menos tiempo.

En la programación cuadrática [Hall70], la ubicación de los bloques se determina a partir de la información obtenida de la lista de redes, y de las posible ubicaciones de los bloques. Así, en la asignación cuadrática la solución para el problema de la ubicación se encuentra hallando los autovalores y autovectores de una matriz construida a partir de la matriz de conectividad entre bloques, y de la matriz de distancia entre posibles ubicaciones de esos bloques. En circuitos de gran tamaño, y en el estilo de diseño de celdas standard, se han aplicado con éxito técnicas combinadas de particionamiento recursivo y programación cuadrática [KSJA91]. Los resultados producidos son comparables en calidad y tiempo a los generados por la técnica del Enfriamiento Simulado [SS95].

El algoritmo de Enfriamiento Simulado (ES) es uno de los métodos de ubicación más desarrollados hasta el momento. La efectividad del ES en la ubicación ha sido probada en diferentes trabajos [KGV83, SS84], y es utilizado por las herramientas de diseño físico comerciales [Tri93]. El ES es un algoritmo de mejora iterativa. Partiendo de una ubicación generada de forma aleatoria se realizan movimientos de intercambio en la posición de los bloques lógicos. Los movimientos son aceptados o rechazados dependiendo de la variación de coste producida. El movimiento se acepta siempre que se produce un decremento en el coste. En caso de que se produzca un incremento de coste, el movimiento se acepta con una probabilidad dada por el factor de Boltzman  $(e^{-\Delta C/T})$ , donde T es un parámetro denominado temperatura. Se suele escoger un valor inicial alto de este parámetro de forma que al principio casi todos los movimientos son aceptados. La temperatura se va disminuyendo según avanza la optimización reduciéndose, de esta forma, la probabilidad de aceptación de movimientos que produzcan incremento de coste. El ritmo de enfriamiento adecuado dependerá, en general, de varios factores como son la naturaleza y tamaño del problema considerado, así como la función de coste elegida. Entre las implementaciones del ES orientadas a la ubicación sobre FPGAs, podemos destacar la herramienta VPR (Versatile Place&Route) [BR97] por la calidad de los resultados que proporciona.

A pesar del éxito del *ES* en la ubicación, existen algunas características del algoritmo que deben tenerse en consideración cuando se afrontan variaciones del problema o se exploran nuevas funciones de coste. Los programas de enfriamiento son específicos, y generalmente no son aplicables directamente a otros problemas y funciones de coste. Debido a esta estrecha relación entre el programa de enfriamiento y el problema o la función de coste considerada, la investigación sobre nuevas funciones de coste para afrontar nuevos desafíos se convierte en una tarea compleja. Por una parte, se requieren costosos estudios experimentales para determinar un programa de enfriamiento adecuado. Por otra parte, en el estudio de nuevas funciones de coste, hay una carencia de soluciones de referencia para validar la adecuación de ese programa de enfriamiento a la función de coste tratada. Puede ser beneficioso, por lo tanto, la investigación de las relaciones subyacentes que pueden existir entre los distintos parámetros que indican el curso o desarrollo de la optimización, y el programa de enfriamiento que hacen que la optimización llegue a buen término. El desarrollo de un programa de enfriamiento autoadaptable a distintos problemas y funciones de coste sería el objetivo último.

#### 2.6.2 Cableado sobre FPGAs

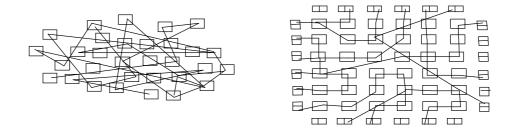

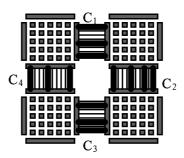

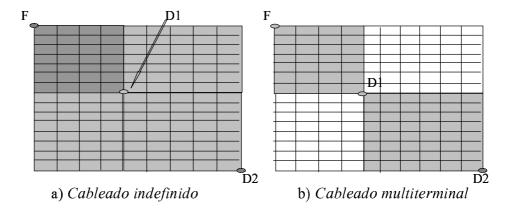

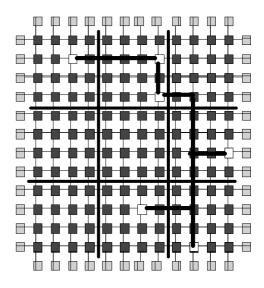

Durante la etapa de cableado correspondiente al ciclo de diseño físico, se establecen las conexiones entre los bloques lógicos mediante la configuración de los recursos de cableado de la FPGA. Si bien este problema es similar al planteado en otros dispositivos como los arrays de puertas y celdas standard, aquí presenta características particulares; por una parte, la anchura de los segmentos de canal es muy limitada, por lo tanto, si no se resuelven los problemas de congestión, el circuito no podrá implementarse en la FPGA [EMHB95]. Por otra parte, los segmentos de canal están unidos entre sí a través de interruptores programables, los cuales incrementan los retardos de las conexiones. Debido a su complejidad combinatoria, el problema del cableado usualmente se resuelve en dos etapas: cableado global y cableado detallado. En la fase de cableado global se asignan segmentos de canal de la FPGA para la conexión de cada red (Figura 2.4) de forma que se cumplan las restricciones en cuanto a la capacidad de los canales. Como veremos más adelante, en el caso de redes

multiterminal como la de la Figura 2.4, el problema es equivalente a la determinación del "Árbol de Steiner Mínimo Rectilíneo", con la particularidad de que la capacidad de los segmentos de canal no debe ser sobrepasada durante el cableado de las redes.

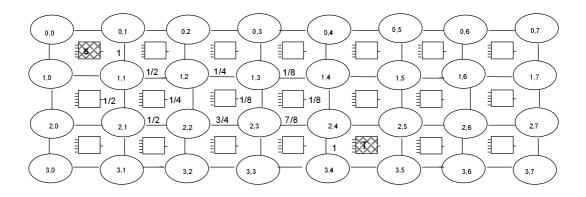

Figura 2.4 Cableado global de una red multiterminal (la retícula sobre la que se realiza el cableado se corresponde con los segmentos de canal de la FPGA)

Podemos distinguir dos tipos de algoritmos para el cableado global atendiendo a cómo se realiza el tratamiento de las redes multiterminal. Por una parte tenemos los algoritmos que descomponen las redes multiterminal en redes de dos terminales. Por otra parte, están los algoritmos que afrontan directamente el tratamiento de las redes multiterminal. Entre los primeros podemos destacar los algoritmos de "El camino más corto", algoritmos de tipo "laberinto", y los algoritmos de "línea de prueba". Entre los segundos, destacan algunos algoritmos de tipo "laberinto" orientados a redes multiterminal, y distintas aproximaciones al "Árbol de Steiner Mínimo Rectilíneo".

Los algoritmos de "El camino más corto" seleccionan el conjunto de vértices que dan lugar a un camino de coste mínimo para una conexión de dos terminales. En los algoritmos de "línea de prueba" [MT68, Hig69] se persigue reducir los requisitos de memoria. Así, el camino recorrido por una red a través de varios segmentos de canal se describe mediante una línea que los englobe, en lugar de detallar todos los segmentos de canal que la componen. En los algoritmos de tipo "laberinto" [Lee61, Sou78, Had75], en una primera fase de exploración, se inician y expanden simultáneamente varios caminos desde el nodo fuente hasta que alguno alcanza el nodo destino. En una segunda fase, se identifica el camino que ha tenido éxito. Existen diversas versiones de este algoritmo, tanto para redes de dos terminales como para redes multiterminal. Las versiones para redes multiterminal producen soluciones de calidad, de forma que es uno

de los métodos más utilizados en la actualidad. Sin embargo, el cableado se hace demasiado lento debido a la gran cantidad exploraciones innecesarias.

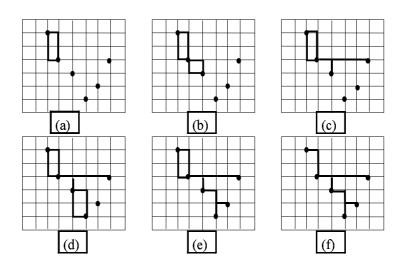

El problema que surge en el cableado global de una red multiterminal, es equivalente al problema del "Árbol de Steiner Mínimo". Éste es un problema NP-completo, y se puede definir como sigue: dado un grafo G(V,E) y un subconjunto  $D\subseteq V$ , seleccionar un subconjunto  $V'\subseteq V$ , de forma que  $D\subseteq V'$ , y tal que V' induce un árbol de coste mínimo. A los elementos del conjunto D se les denomina puntos de demanda, mientras que los elementos del conjunto D'D constituyen los puntos de Steiner [She99]. Al Árbol de Steiner Mínimo para una métrica rectilínea se le denomina Árbol de Steiner Mínimo Rectilíneo (ASMR). Este problema es también un problema NP-completo. Existe una interesante relación entre el ASMR y el Árbol de Expansión Mínima (AEM) [Hwa76] que viene dada por la Ecuación 2.8.

$$\frac{L_{AEM}}{L_{ASMR}} \le \frac{3}{2} \tag{2.8}$$

Como consecuencia de esta relación, muchas aproximaciones para resolver el *ASMR* están basadas en el cálculo del *AEM* [LBH76, HVW90, KZ97, MVG99]. De la misma forma, el *AEM* se utiliza habitualmente como referencia para comparar las distintas aproximaciones al *ASMR*. Así, el porcentaje de mejora M sobre el *AEM* se puede determinar mediante la Ecuación 2.9.

$$M = \frac{L_{AEM} - L_{ASMR}}{L_{AEM}} x 100 \tag{2.9}$$

Hasta la fecha, ha destacado la aproximación *Batched Iterated 1-Steiner* (BIIS) [GRSZ94, Rob] por la calidad de las soluciones obtenidas, encontrándose éstas, en valores medios, a un 0.5% de los valores óptimos [MVG99]. Sin embargo, los tiempos de cómputo de éste y otros algoritmos como el IRV [MVG99], basado en programación lineal entera, son todavía excesivos para redes con un número elevado de nodos. La

lentitud de estos algoritmos se ha puesto de manifiesto recientemente con el desarrollo del algoritmo *Geosteiner* [WWZ98] que permite el cálculo del *Árbol de Steiner Mínimo Rectilineo* de forma exacta en tiempos comparables a los de BI1S.

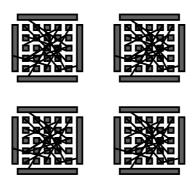

La segunda etapa que permite completar el rutado del circuito es la del cableado detallado (Figura 2.5). Durante esta fase se especifica qué cables, pertenecientes a cada segmento de canal, se utilizan para la conexión de cada red con las restricciones impuestas por el cableado global. El problema del cableado detallado normalmente se resuelve de forma incremental. El orden de rutado de las regiones se establece siguiendo diferentes factores como la pertenencia de una determinada red al camino crítico, o el número de redes que pasan a través de una región.

Figura 2.5 Cableado detallado de una red. Se especifica qué cables de cada segmento de canal se utilizan en la conexión. (R.Xilinx)

Por último, debemos mencionar la técnica de cableado de "ripup and reroute" [CLWL95, BR97], que es complementaria de cualquiera de las anteriores. Esta técnica se aplica habitualmente cuando no es posible rutar más redes debido al agotamiento de los recursos de interconexión, bien durante el cableado global o bien durante el cableado

detallado. Su objetivo es aliviar la congestión levantando las redes que entran en conflicto, y variando el orden en el que son rutadas.

Entre los trabajos publicados para el cableado de circuitos sobre FPGAs podemos citar una serie de herramientas como son CGE, SEGA, TRACER-fpga, GBP, OGC, IKMB, FPR, y VPR.